基于EMIF接口的數據采集系統的設計

3 硬件電路設計與實現

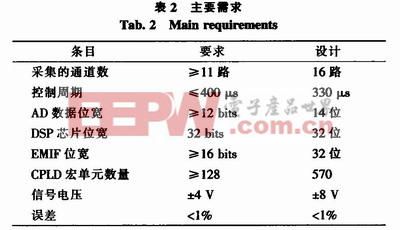

3.1 需求分析

本設計硬件任務主要是完成對主電路的電壓、電流的采集,具體的要求如表2所示。本文引用地址:http://cqxgywz.com/article/150954.htm

3.2 硬件設計

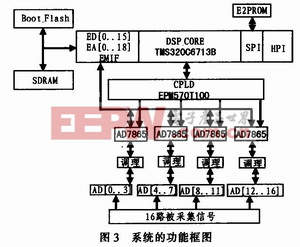

圖3所示是TMS320C6713外圍的主要的功能框圖。

如圖3所示,本設計的外圍器件主要包括:雙口RAM,用于與定點核DSP芯片(如TMS320F2812)交換數據;Boot Flash,當程序的大小大于192 KB,用于存儲啟動程序;SDRAM,用作運行部分程序的存儲介質;CPLD,用于邏輯擴展;AD7865,用于采集電壓電流的實時數據。

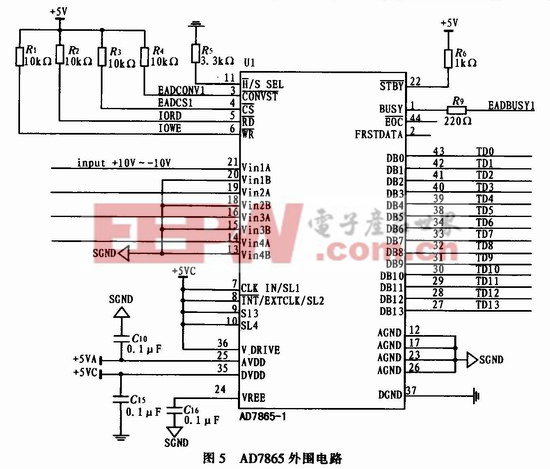

AD7865是一種高速、低功耗、四通道同步采樣的14位A/D轉換芯片,該芯片內部有1個2.4μs的逐次逼近型A/D轉換器,4個跟蹤/保持放大器,內部2.5V參考電壓,同時片上還集成有時鐘振蕩器和1個高速并行接口。AD7865可大大簡化硬件電路設計。AD574轉換時間為25μs,而AD7865完成四通道信號的同時轉換,則只需要100 μs。 AD7865內部4個采樣通道的輸入信號是同步采樣的,只需發送1個脈沖的采樣啟動信號,芯片將自動完成采樣、逼近和存儲數據到片內特定寄存器等工作,單路采樣速率350 KSPS,四路同時采集時100 kHz。

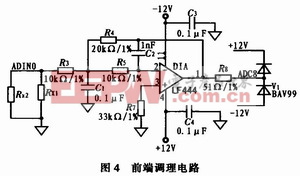

根據設計需求可設定調理電路放大倍數為2倍(反相放大),則實際值與A/D的采樣值之間的關系可由式(1)表示。

實際值=采樣值/213x10/(-2)×傳感器系數 (1)

若采樣值為正數時可用式(1),否則需先進行求補處理。

AD7865的前端調理電路如圖4所示。

AD7865的外圍連接電路如圖5所示。

TMS320C6713的EMIF接口各信號線可以根據EMIF接口的示意圖(圖2)連接。在這里需要注意的是各信號線的上拉、下拉和信號線上的限流等措施。可按照如下原則設計:1)地址線和數據線以及控制線出口處可以串聯33 Ω的電阻,以達到限流的效果;2)對于某些敏感信號(如片選/CEx信號,保有信號/HOLD等等)在默認狀態下的電平,應該通過上拉和下拉進行確定。一般情況下,上拉電阻用10 kΩ的電阻,下拉電阻用1 kΩ的電阻。

CPLD的主要功能主要是實現邏輯擴展,在本設計中,CPLD的主要工作是在DSP6713和多片AD7865芯片之間進行信號的解析和傳遞。選用的CPLD芯片是ALTERA公司的EPM570,該芯片相較于其他同類型的CPLD而言,配置簡單、存儲容量大而價格較低廉。其外圍電路比較簡單,可以參考ALTERA公司關于該芯片的引腳功能表,在此不做贅述。

評論