一種新型的多DSP紅外實時圖像處理系統設計

1.2.2 擴展存儲器接口

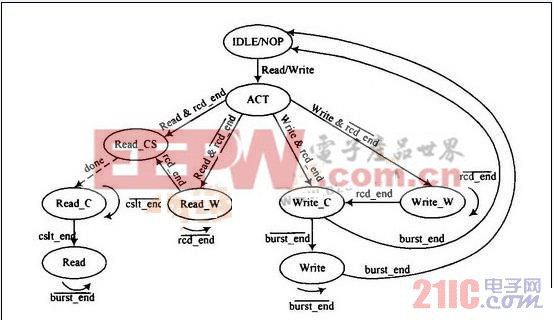

FPGA外接SDRAM做為外擴存儲器。SDRAM芯片選用HY57V561620,該芯片為16位的SDRAM,工作頻率為100 MHz。SDRAM工作狀態轉換圖如下:

圖2 SDRAM工作狀態轉換圖

1.2.3 與視頻顯示電路接口

顯示電路中選用的數/模轉換芯片為ADI公司的ADV7122芯片,該芯片為三通道10 b的視頻數/模轉換芯片。

1.3 四端口存儲器電路設計

四端口存儲器使用IDT公司的IDT70V5388芯片。該芯片為64K×18 b的同步四端口存儲器,4個端口可同時對存儲器的任何地址進行操作,每個端口的最大輸出速率為200 MHz,因此4個端口總的數據帶寬為14 Gb/s。

存儲器每個端口都設置有郵箱中斷功能,這一功能能夠很好地實現與各個端口相連器件的相互通信。選擇郵箱中斷功能后,每個端口給分配一個郵箱,當某一端口向其他端口的郵箱寫入數據時,該端口將會產生郵箱中斷。PORT1向PORT2的郵箱地址(0xFFFE)進行寫操作,PORT2將產生郵箱中斷,PORT2對該郵箱地址進行讀操作之后清除郵箱中斷。

1.4 DSP電路設計

DSP芯片選用Ti公司的TMS32C6414 EGLZA6E3,其主頻為600 MHz。TMS320C6414是TI公司高性能的定點DSP。該芯片采用超長指令字結構(VLIW),每個時鐘周期可以執行8個32位指令。

2 系統工作流程及軟件設計

系統上電后,DSP1從與其連接的FLASH芯片中讀出非均勻性校正算法所需的系數,傳送給FPGA,FPGA對圖像進行校正,校正結果寫入四端口RAM,圖像拉伸顯示模塊和數字圖像記錄模塊。3個DSP可以從四端口RAM中讀取圖像信息,并行進行圖像處理工作。

評論