Niosll和USB接口的高速數據采集卡設計

2.2 主控電路FPGA芯片

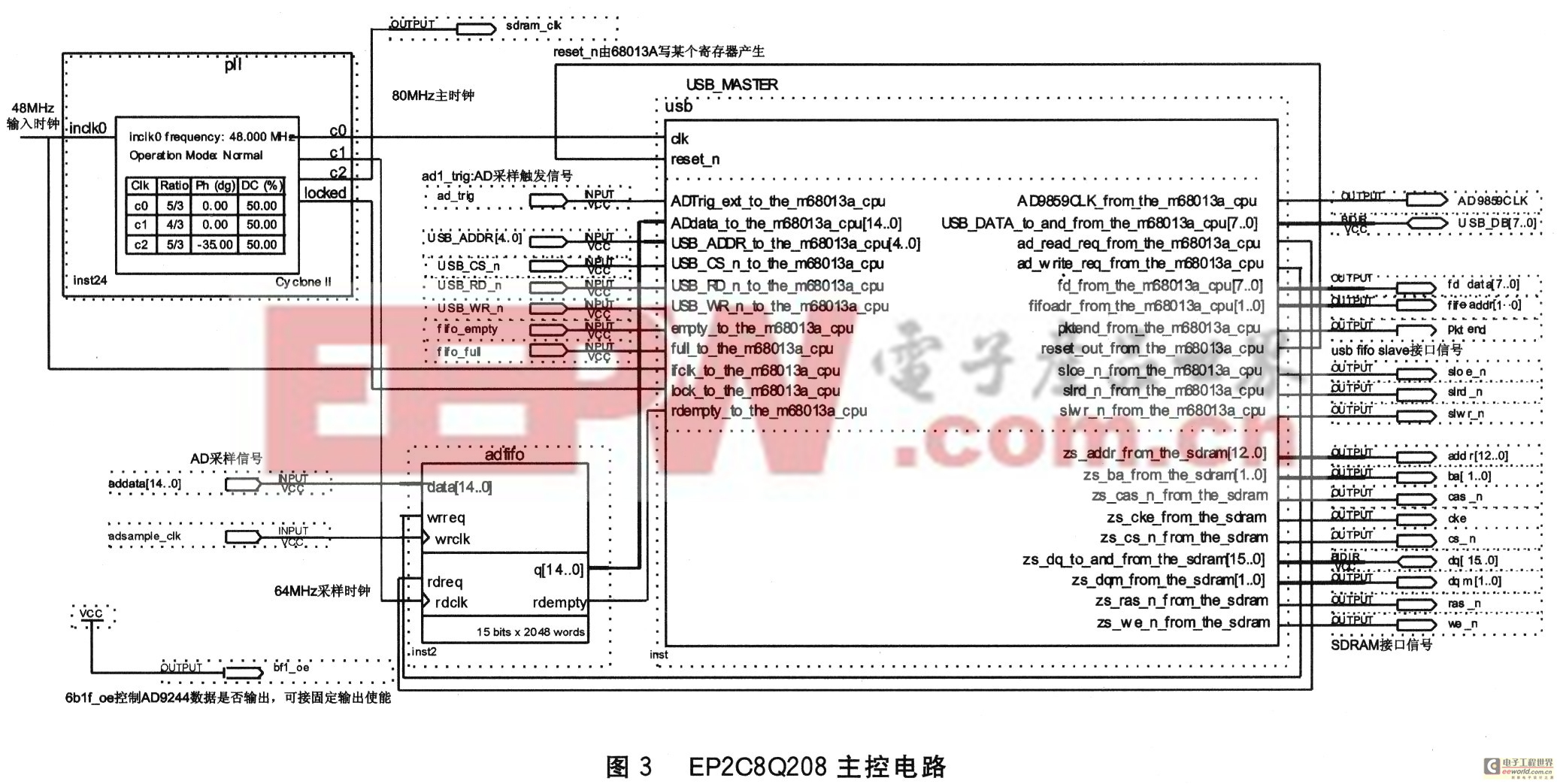

EP2C8Q208EP2C8Q208主控電路如圖3所示。

FPGA芯片也是一種特殊的ASIC芯片,屬于可編程邏輯器件,它是在PAL、GAL等邏輯器件的基礎上發展起來的。同以往的PAL、GAL等相比,FPGA規模比較大,適合于時序、組合等邏輯電路應用。本文選用A1tera公司的FPGA芯片EP2C8Q208,完成數據采集卡的時序和地址譯碼電路設計。由于EP2C8Q208有36個M4K RAM,在FPGA內部設計一個16位寬度、4 KB深度的FIFO,使用FIFO提高數據采集卡對多通道信號的采集存儲能力。FIFO有半滿、全滿、空標志位,當檢測到半滿標志位時,FIFO同時讀寫;全滿時只讀不寫;空時只寫不讀。A/D采樣控制信號通過FPGA控制;PC機對采集后的數據作進一步處理,以提高精度,其中2選1模塊,由主控制模塊來控制,選擇是直接將采集數據送給PC機處理,還是在內部進行DSP處理后再送給PC機。

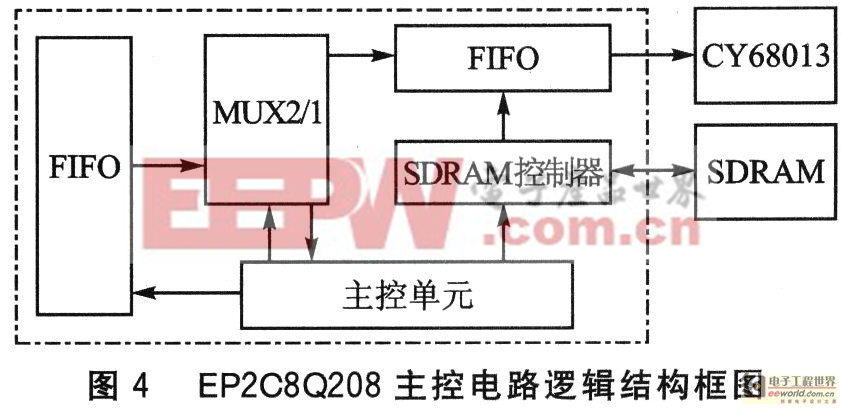

由于Nios是一個位于FPGA中的處理器軟核,定制其外設就顯得比較容易,在SOPC Builder(集成到Quartus II工具中的為建立SOPC系統設計,提供標準化的圖形設計環境。其由CPU、存儲器接口、標準外圍設備和用戶自定義的外圍設備組成)環境下,其定制邏輯的結構框圖如圖4所示。

評論