用CPLD實現嵌入式平臺上的實時圖像增強

對于連續圖像P,其局部邊緣可由對應空間梯度的幅值

,取其一階近似ΔPi,j=2Pi,j-Pi,j-Pi-1,j,可得圖像{Pi,j|i=1,2,...,n;j=1,2,...,m}在(i,j)的邊緣信息

如果不計Pi,j的取值范圍,可直接對圖像{Pi,j|i=1,2,...,n;j=1,2,...,m}進行修正:

P′i,j=Pi,j+ΔPi,j,

其中,P′i,j表示Pi,j修正后的值顯然,圖像{Pi,j|i=1,2,...,n;j=1,2,...,m}按此規則修正后邊緣值的變化更為強烈,邊緣更為突出,可達到邊緣增強的效果同時,由于在原圖像上疊加了梯度值,使得修正后的圖像的頻譜有一定的擴展但由于沒有對Pi,j的取值作約束, 這樣處理后的象素值可能會溢出,例如對于每個色彩通道為8位的圖像,處理后的數值可能會大于255或小于0因此,通常要對其進行歸一化處理,即:

Pnew=255%26;#215;(P′-P′min)/(P′max-P′min)

但用硬件實現乘除運算可能會占用很多資源,上述公式即便以運算實現都是很不經濟的本文采用預拉伸加飽和/截止的方法,在不犧牲頻率特性的基礎上達到減少計算量的目的

考察ΔPi,j與Pi,j的直方圖,分別取得它們的右峰值所對應的橫座標,記為GΔ和G,并找到k,使得kGΔ+G=255,則修正公式變為P′ i,j=Pi,j+kΔPi,j其中kΔPi,j可以LUT實現修正后的P′i,j可在[0,255]上進行飽和/截止運算

2 用CPLD實現實時的圖像增強

本文所采用的改進圖像增強算法的主要成份是差分累加以及飽和/截止這些運算都是加減法及邏輯運算,都屬于ALU的簡單操作,適合硬件實現本文采用 CPLD實現所提出的算法以對具有30fps的1280 1024 RGB圖像計算ΔPi,j為例,每計算一點ΔPi,j需要4次加(減)運算,即總的需要1280 1024 5;3 30 4=471,895,200次加(減)運算如果采用的DSP的速度是100MHz,且假定所有運算都是單周期的,則僅僅該運算就需要4.7s!所以采用 CPLD實現某些運算是必需的

圖3 圖像增強算法的硬件實現結構

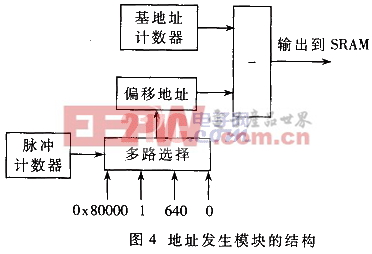

采用CPLD實現運算(例如邊緣處理中涉及的求梯度運算),還需解決數據的暫存問題本文以一片高速SRAM作為數據緩沖區由于圖像數據的采樣輸入的頻率也很高,需要充分合理地安排好每一次操作的時序,充分利用已參與運算的數據及中間結果,減少數據進出SRAM的次數

2.1 基于E1-DSP的網絡圖像采集平臺

在分析具體實現方法前,先簡要介紹所采用的硬件平臺該平臺主要用于遠程圖像采集和以太網傳輸,其圖像通道結構如圖1所示

OV9620是CMOS的數字圖像傳感器,負責采集連續的數字圖像;中央處理器使用德國HYPERSTONE公司的E1系列RISC DSP,它集DSP和RISC于一身,可以加載OS,方便地實現任務調度內存管理等功能,大大提高系統的總體性能;CPLD的基本功能是作為E1總線接口控制模塊,本文還將用它實現圖像增強運算

2.2 算法的總流程

為了實現實時的讀寫和運算,需要由外部電路產生24MHz%26;#215;4的時鐘EXCLK作為讀寫時鐘,所有時序都由CMOS時鐘和EXCLK控制,可以做到完全同步具體流程如圖2所示

(1)在CMOS時鐘到來時,從CMOS傳感器的數據輸出口采集Pi,j,并實現加法運算RESULT=Pi,j+Pi,j,同時用EXCLK的第0個時鐘向SRAM寫入P′i,j-1或P′i,m-1 (本行最后一個數據,下一次操作應換行);

(2)在EXCLK的第1個時鐘鎖存RUSELT,由SRAM讀入Pi-1,j,并做減法運算RESULT=RESULT-Pi-1,j;

(3)在EXCLK的第2個時鐘鎖存RUSELT,由SRAM讀入Pi,j-1,并做減法運算RESULT=RESULT-Pi,j-1;

(4)在EXCLK的第3個時鐘鎖存RUSELT,同時寫入Pi,j

評論