基于FPGA和VHDL語言的多按鍵狀態識別系統

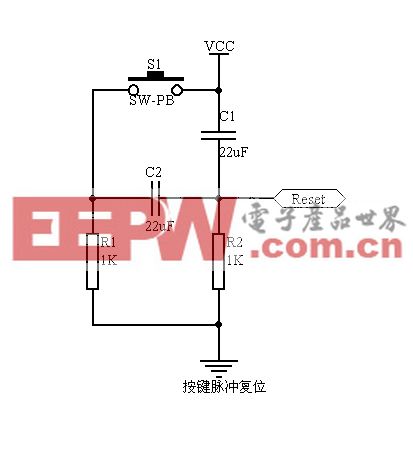

2.2 按鍵電路

圖3為一路按鍵電路,共60個按鍵(i=1~60)。由于外界環境復雜,按鍵引線長達6 m,保護二極管VDi:在外界干擾信號大于VCC時導通起到保護FPGA的作用。電阻Ri上拉限流,按鍵未閉合狀態下FPGA輸入引腳始終處于高電平。

3 FPGA內部邏輯設計

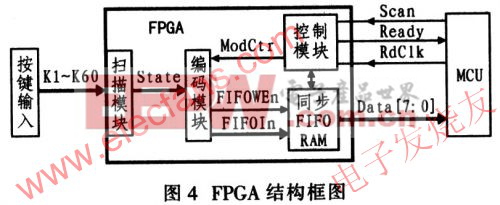

FPGA內部功能分為掃描模塊、編碼模塊、控制模塊以及同步FIFO RAM模塊,如圖4所示。

圖4中,K1~K60為60個按鍵的輸入端,Scan為工作模式選擇信號,Ready為讀準備好信號,RdClk為讀時鐘信號,Data[7:0]為數據輸出,ModCtr為編碼模式控制信號,FIFOWEn為FIFO RAM寫使能信號,FIFOIn為FIFO RAM數據輸入,State為按鍵狀態掃描信號。其工作原理為:掃描模塊周期掃描按鍵狀態,其結果送入編碼模塊;編碼模塊根據模式控制信號ModCtr選擇編碼方式編碼,將其結果送入FIFO RAM;控制模塊產生對FIFO RAM的讀取控制信號;MCU可通過Readv、RdClk控制信號讀取Data[7:0]數據線上的按鍵編號和狀態數據。

3.1 掃描模塊

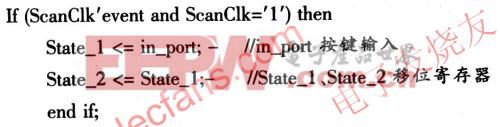

掃描模塊主要完成掃描按鍵狀態輸入和按鍵的軟件去抖動。掃描按鍵狀態輸入是以5 m8為周期掃描60個輸入引腳,將其結果存入60個兩位狀態移位寄存器。其代碼為:

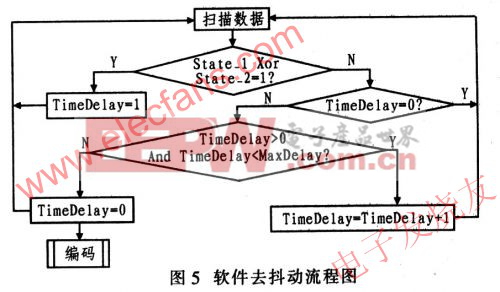

按鍵去抖有硬件和軟件2種實現方式。為了節省成本,充分發揮FPGA器件的功能,該系統設計采用軟件去抖。圖5為軟件去抖動流程。圖中State為2位狀態移位寄存器,初始值為0,TimeDelay為延時計數器。

評論