高清晰LCD HDTV中使用Cyclone III FPGA技術

Nios 嵌入式處理器

出于多種考慮,設計人員在實現控制功能上沒有采用硬件邏輯( 通常以狀態機的形式),而是轉向Nios®II 嵌入式處理器。首先,其設計調試要比HDL 簡單。除了簡化開發之外,設計人員還希望CPU 和工具包能夠通用,適合多種應用。而且,Nios II 軟核處理器是性價比非常高的解決方案,不需要外部處理器,設計人員可以把它嵌入到現有FPGA 設計中,沒有額外成本。

對于DTV 應用,Nios II 處理器控制所有的數據流,包括:

將視頻流送至顯示屏

遠程控制處理

常規的管理任務

處理條件訪問接口,例如智能卡等

從視頻流中解密控制字

FPGA 的優點

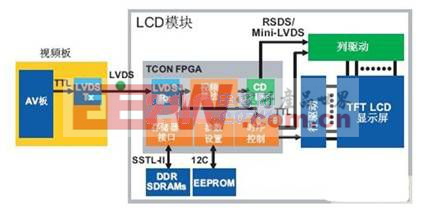

LCD HDTV 的核心是其圖像處理和時序控制模塊( 如圖2 所示)。圖像處理模塊通常包括掃描速率轉換器、幀速率轉換器、色彩解碼器、移動探測、scalar 和去隔行等功能。

圖2. 典型的LCD 電視接口結構圖

評論