基于DDS跳頻信號源的設計與實現

2.1 邏輯地址控制單元

在本設計中,邏輯地址控制單元由一個6級移位寄存器和6位存儲器構成。系統時鐘clk經過64分頻后得到時鐘clk_64,將clk_64作為邏輯地址控制單元的驅動時鐘。當一個時鐘clk_64上升沿到來時,r(1:5)=r(0:4)同時

2.2 DDS單元

DDS單元為本設計的核心,由相位累加器和ROM查詢表兩部分組成。在頻率控制字(5:0)的控制下產生相應頻率的信號。

2.2.1 相位累加器

相位累加器是DDS的重要的組成部分。被用來實現相位的累加,并將其累加結果存儲。如果相位累加器的初值為φ0,則經過一個時鐘周期后相位累加器值為φ1,即φ1=φ0+k,其中k為頻率控制字。當經過n個時鐘周期后φn=φ0+nk。可見φn為一等差數列。

在本文中基于FPGA的相位累加器設計如圖2所示。從圖2中可以看出,相位累加器由一個數字全加器和一個數字存儲器構成。為了提高DDS輸出頻率的分辨率,一般要求n足夠大,這樣就要求ROM中存儲大量數據。但是考慮到硬件資源有限,所以在相位累加器中采用了截短處理,這樣既可保證較小的頻率分辨率,又節省了硬件資源。

2.2.2 ROM查詢表

ROM中所存儲的數據是數字波形的幅值,在一個系統時鐘周期內,相位累加器將輸出一個位寬為L的序列對其進行尋址,經過低通濾波器后得到所需要的波形。若相位累加器的輸出序列的位寬L=16,ROM中存儲的數據位寬為M=16,可以計算出ROM的存儲量為2L×M=1048576bits,雖然一塊FPGA開發芯片上提供了大量的ROM,可以顯著提高輸出信號頻率精確度和信號幅值準確性,但這樣會使成本提高、功耗增大。

在保證輸出信號具有良好頻率分辨率的前提下,以產生正弦信號為例,考慮到基于DDS產生的正弦波具有周期性,因此本設計的ROM中存儲1/4周期正弦波。如圖2所示為存儲1/4周期正弦波形ROM查詢表設計。利用正弦信號的對稱性,通過改變ROM存儲器地址及對其輸出端控制,最終得到整周期正弦信號。

3 仿真結果及分析

3.1 DDS單元仿真結果及分析

3.1.1 仿真參數

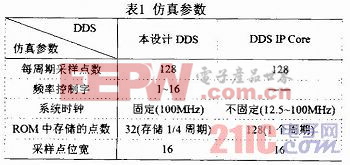

為分析本設計中DDS所產生頻率的精確度,現使用Xilinx ISE 8.11中DDS IP Core進行對比,在同等仿真參數條件下,分別對本設計的DDS和DDS IP Core進行仿真測試。表1中分別給出基于本設計DDS和DDS IP Core的仿真參數。本文引用地址:http://cqxgywz.com/article/155539.htm

3.1.2 仿真結果及分析

如圖3所示,clk是系統時鐘,new_dds_sine為在頻率控制字k=16時基于本設計DDS產生的頻率為1.5625MHz(理論值)的正弦波,dds_ip_ core_sine為基于DDS IP Core產生的頻率為1.5625MHz(理論值)的正弦波。

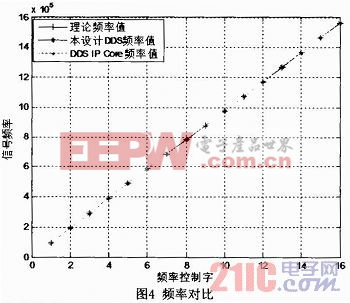

圖4給出在k為1~16時,本設計的DDS所產生信號的頻率和DDS IP Core所產生信號的頻率與理論頻率值的對比。從圖中可以看出,本設計DDS所產生的信號頻率與理論頻率值比較接近,且本設計DDS中ROM查詢表中存儲的點數少,從硬件的角度考慮更加節省資源,能耗更低。

評論