基于固態存儲技術的DRFM設計

2.1 中頻采集模塊設計

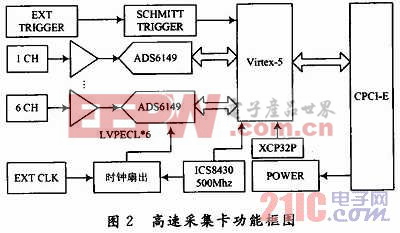

中頻信號采集模塊主要是完成中頻信號的模/數轉換,并將轉換后的數據通過FPGA處理后傳輸給存儲模塊。主要由前端調理電路、6片高速ADC、時鐘分配電路、FPGA、電源五部分組成,前端信號調理電路主要是完成信號的放大或者是衰減,以匹配A/D的輸入要求,高速ADC完成模數轉換,FPGA負責接受A/D的數據和傳輸以及整塊板卡的控制。其構成框圖如圖2所示。本文引用地址:http://cqxgywz.com/article/156272.htm

該設計的高速ADC采用TI公司的高速ADC即ADS6149。ADS6149是一款高性能的14位,250 Mb/s采樣率模/數轉換器,它提供出色的高模擬帶寬和低輸入抖動,在高頻信號輸入時,ADC提供極高的SNR和SFDR指標,其內部包括可編程增益設置,可以用于提高小信號輸入時的SFDR性能。時鐘對于高速ADC系統而言尤其關鍵,這是因為時鐘信號的時序準確性可以直接影響ADC的動態特性。該設計選用ICS834061,它是一款集成高頻時鐘發生器,在單芯片中集成整個鎖相環系統和時鐘扇出系統,外圍器件只要1個晶振,具有2路LVPECL時鐘扇出,輸出頻率范圍20~500 MHz可調,時鐘抖動最大只有6 ps,能滿足該設計的要求。

2.2 中頻還原模塊設計

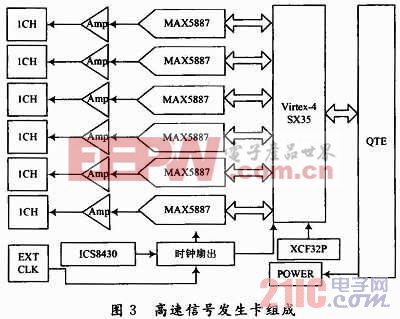

中頻信號還原模塊完成處理后的信號的還原,主要由FPGA、高速DAC、后端調理電路、時鐘分配電路、控制信號發生電路,電源6部分組成,其中FPGA負責將處理之后的數據發給D/A轉換器以及整塊中頻還原卡的控制。高速ADC完成模/數轉換功能,后端調理電路提供A/D轉換后的濾波和信號放大功能,時鐘電路為系統提供高精度、低抖動的時鐘信號,其構成框圖如圖3所示。

評論