基于FPGA+DSP的多串口數據通信的實現

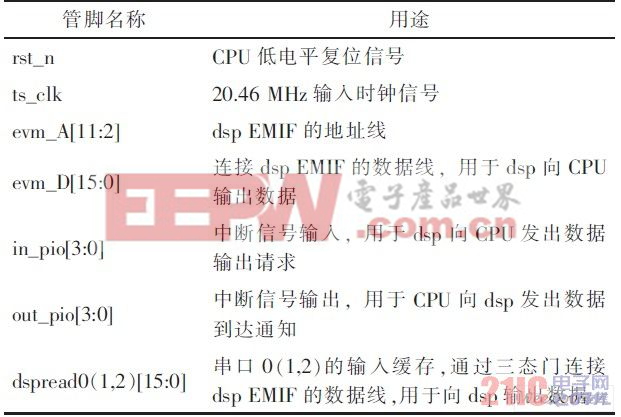

圖3是NIOS II CPU在Quatus中的連線示意圖,即位于中心的inST6模塊。該CPU主要管腳定義如表1所示。

圖3 NIOS II CPU在Quatus中的連線示意圖

表1 CPU主要管腳定義

值得說明的是,ts_clk輸入時鐘20.46 MHz即為NIOS IICPU的時鐘頻率,串口波特率為115 200 bps,可由該時鐘分頻得到。DSP6713的EMIF為輸入輸出雙向32位,在本設計中串口部分僅使用低16位,使用三態門來控制數據流向。三態門輸入輸出的使能信號是dsp給出的ce空間使能信號ce_6713。

串口輸入數據先由NIOS II CPU寫入每個串口的輸入緩存,當滿足條件時由out_pio管腳向dsp發出中斷,用以告知其可以讀取相應串口的數據了,緩存的數據由dspread0傳遞至三態門tri_16.dsp讀取時三態門為dsp輸入方向,dsp的EMIF數據線evm_D隨即出現數據,配合EMIF地址線evm_A即可完成串口輸入數據向dsp傳遞;當dsp有數據要經串口輸出時,數據由dsp的EMIF數據線evm_D輸入,dsp通過in_pio向NIOS II CPU發出中斷信號,請求發送數據。詳細的發送接收流程見下文。

2 軟件設計

NIOS II CPU的控制代碼部分分為主函數和各種中斷響應函數。在主函數里完成寄存器初始化、各串口數據輸出的任務。串口的中斷響應函數則主要完成數據的輸入任務。

為了便于FPGA和DSP之間的控制信息交換,每個串口設有地址固定的長度各為32位(4字節)的輸入和輸出兩個控制寄存器。通過對各標志位的讀寫操作即可實現系統對各串口的控制。串口的輸入控制寄存器定義見表2,輸出控制寄存器與之類似。

評論