利用串行RapidIO實現FPGA協處理

SRIO系統應用實例

1.嵌入式系統:像x86這樣的CPU結構是針對那些無需進行大量乘法運算的一般應用優化過的 相比而言,DSP結構則是針對包括濾波、FFT、矢量乘法和查找以及圖像或視頻分析等信號處理操作優化過的

相比而言,DSP結構則是針對包括濾波、FFT、矢量乘法和查找以及圖像或視頻分析等信號處理操作優化過的

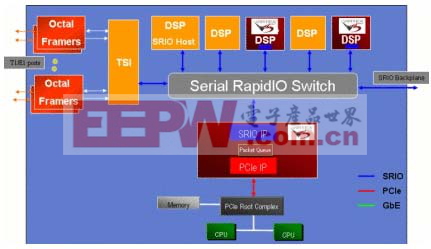

因此,同時采用CPU和DSP的嵌入式系統可以輕松利用通用處理器和信號處理器兩種結構的優勢 圖6給出了一個此類系統的例子,其中同時包含FPGA、CPU和DSP架構

圖6給出了一個此類系統的例子,其中同時包含FPGA、CPU和DSP架構

圖6:基于CPU的高性能DSP子系統

在高端DSP中,串行RapidIO已成為主流數據互連方式 x86 CPU中主要的數據互連則采用PCI Express實現

x86 CPU中主要的數據互連則采用PCI Express實現 如圖6所示,對FPGA進行一些簡單的配置,就能用它調整DSP應用的規模,和/或橋接幾種完全不同的互連標準(如PCI Express 和串行RapidIO)

如圖6所示,對FPGA進行一些簡單的配置,就能用它調整DSP應用的規模,和/或橋接幾種完全不同的互連標準(如PCI Express 和串行RapidIO)

在該系統中,管理PCI Express系統的是Root Complex芯片組,SRIO系統則受一塊DSP管理 PCIe的32/64位地址空間(基地址)可自動映射至34/66位SRIO地址空間(基地址)

PCIe的32/64位地址空間(基地址)可自動映射至34/66位SRIO地址空間(基地址) PCIe應用程序通過內存或I/O讀寫與Root Complex芯片組通信

PCIe應用程序通過內存或I/O讀寫與Root Complex芯片組通信 這些事務均可通過流寫入、原語和確認讀/寫事務(SWRITEs

這些事務均可通過流寫入、原語和確認讀/寫事務(SWRITEs ATOMIC

ATOMIC NREADs

NREADs NWRITE/NWRITE_Rs)等I/O操作輕松映射至SRIO空間

NWRITE/NWRITE_Rs)等I/O操作輕松映射至SRIO空間

在Xilinx的FPGA中設計此類橋接功能非常簡單,因為PCI Express的后端接口和串行RapidIO端點的功能模塊是類似的 分組隊列模塊隨后就可以實現從PCIe到SRIO或從SRIO向PCIe的轉換,從而在這兩個協議域之間建立數據流

分組隊列模塊隨后就可以實現從PCIe到SRIO或從SRIO向PCIe的轉換,從而在這兩個協議域之間建立數據流

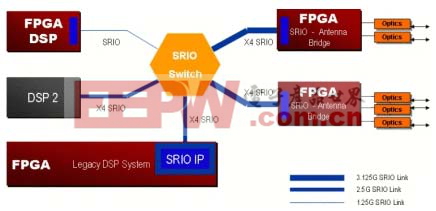

2.DSP處理應用:在那些DSP處理是主要架構要求的應用中,系統結構可按圖7所示方式設計

圖7:需要強大DSP處理能力的器件

Xilinx Virtex-5 FPGA在該系統中就可用作其他DSP器件的協處理器 如果用SRIO進行數據互連,這整套DSP系統方案還可輕松實現調整

如果用SRIO進行數據互連,這整套DSP系統方案還可輕松實現調整 這樣的方案具備可擴展性,適應未來的發展,而且還能以多種外形尺寸實現

這樣的方案具備可擴展性,適應未來的發展,而且還能以多種外形尺寸實現

當需要強大DSP功能的應用還需要進行快速大量的復雜運算或數據處理時,可以將這些處理任務卸載至x86 CPU中去運行 Xilinx Virtex-5 FPGA允許對PCIe子系統和SRIO結構進行橋接,從而實現高效的功能卸載

Xilinx Virtex-5 FPGA允許對PCIe子系統和SRIO結構進行橋接,從而實現高效的功能卸載

3. 基帶處理系統

隨著3G網絡快速成熟,OEM廠商將會采用新的外形尺寸的器件和設備來減少容量和覆蓋方面的問題,使用SRIO并基于FPGA的DSP架構正是應對此類挑戰的絕佳方案 傳統DSP系統也可重新調整為這種快速低功耗的基于FPGA的結構,以便充分利用FPGA的可調整性優勢

傳統DSP系統也可重新調整為這種快速低功耗的基于FPGA的結構,以便充分利用FPGA的可調整性優勢

在此類系統中,如圖8所示,FPGA可以在滿足天線業務線速處理要求的同時通過SRIO為其他系統資源提供連接 而由于串行RapidIO協議提供的速度和帶寬均很高,所以那些內部固有低速并行連接的現存傳統DSP應用要移植到這類系統中也很簡單

而由于串行RapidIO協議提供的速度和帶寬均很高,所以那些內部固有低速并行連接的現存傳統DSP應用要移植到這類系統中也很簡單

圖8:基帶處理

本文小結

串行RapidIO正在越來越多的新應用中嶄露頭角,特別是在采用DSP的有線和無線應用中 在Xilinx器件中實現串行RapidIO主要有以下優勢:

在Xilinx器件中實現串行RapidIO主要有以下優勢:

1. Xilinx提供了完整的SRIO端點方案;

2. 可利用同樣的軟、硬件結構,通過靈活的調整,實現不同類型的產品;

3. 由于Xilinx器件采用了新型GTP收發機和65nm 技術,因此功耗很低;

4. 通過CoreGen GUI 可實現方便的可配置性和靈活性;

5. 由于業界領先的廠商都有器件支持SRIO連接,因而硬件互通性有保證;

6. 可通過使用PCIe和TEMAC等集成IO模塊實現系統集成,從而降低系統整體成本

評論