基于低噪音單芯片高頻分頻器的PLL設計

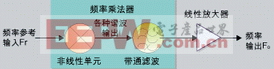

圖2所示為一個標準的頻率乘法器。它的原理是:將一個穩定的頻率源送入非線性的電路中,然后選擇性地產生想要的諧波輸出。這一輸出經過嚴格的濾波,然后通過線性放大器重新放大,進行損失補償。

由于諧波級數越高其輸出越低,為了將頻率從一個低階的參考源(如晶振)升高到微波頻率,我們需要多級電路。這就是頻率乘法器的缺點,它常常使設計變得非常復雜而且昂貴,且效率卻很低。另一方面,乘法器也有其優點,那便是它幾乎可以達到任何想要的高頻。

新一代的低噪音高頻單芯片分頻器為RF設計者提供了一種低成本的高性能解決方案,可用來取代頻率乘法器。采用Zarlink提供的13.5GHz分頻器,設計者可通過成本較低的鎖相環(PLL)電路為VSAT和其它RF器件構建高頻源。分頻器可擴展單芯片頻率合成器的輸出范圍,從而保證工作于高頻的 PLL的相關正向設計得以順利進行。

圖3是一個基頻合成器電路,它由一個壓控振蕩器(VCO)、一個可變分頻器和一個相位比較器構成。

加在VCO上的控制電壓決定了VCO的輸出頻率。相位比較器產生的電壓與兩個輸入信號的相位差成比例。這一電壓控制著VCO的頻率,從而保證通過分頻器后(fN)從VCO反饋回來的相位比較器輸入頻率與參考輸入fr的相位一致,以此保證頻率相同。因此,VCO的頻率保持為N×fr。這樣的合成器將生成一系列間隔為fr的頻率。

單芯片頻率合成器的最大范圍通常限制在2-3GHz,一方面是受市場決定,另一方面則因為頻率太高時合成器的功耗會過大。為了產生高頻源,合成器通常在PLL中與一個獨立的外部分頻器進行耦合。這個分頻器將頻率源“預分”到一個可被合成器處理的頻率。

PLL價廉物美,但目前為止,它們的最大頻率受低噪音商用分頻器的頻率響應限制。

分頻器相關文章:分頻器原理

評論