基于DDS技術的動態偏振控制器驅動電路研究

圖2光纖擠壓器偏振態隨電壓變化的邦加球示意圖由此可知,只要輸入光的偏振態與F1和F2的方向都不垂直,則輸入光的偏振態都可以通過操作至少2個擠壓器改變到任意一個偏振態。

2 DPC的驅動電路設計

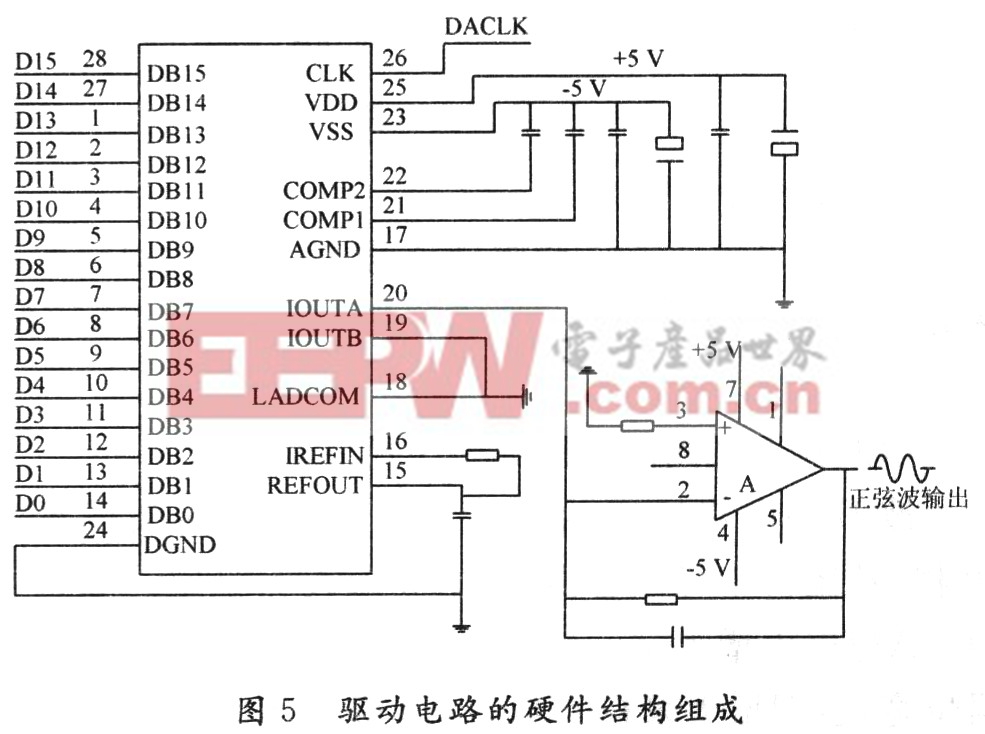

DPC驅動電路的設計基于DDS技術,系統主要由Xilinx Spartan-3系列FPGA、數/模轉換器LTC1668及寬帶放大器LT1812組成。

2.1 DDS的基本原理

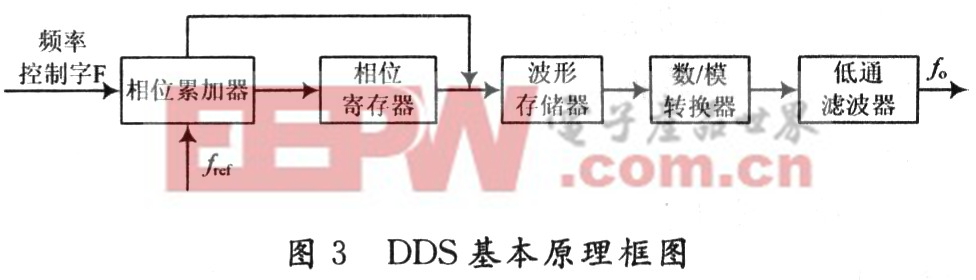

DDS的基本原理是基于采樣定理。將相位累加器輸出的相位碼通過查表法映射成波形幅度碼,經模/數轉換和低通濾波后產生波形,其框圖如圖3所示。它主要由參考時鐘fref、相位累加器、相位寄存器、波形存儲器、數模轉換器及低通濾波器等部分構成。

DDS工作時,它將在時鐘脈沖的控制下,對頻率控制字F用累加器進行處理,以得到相應的相位碼;然后由相位碼尋址波形存儲器進行相位碼――幅度編碼變換后輸出不同的幅度編碼;再經過數模轉換器和低通濾波器處理,即可得到由頻率控制字決定的連續變化的輸出波形。

2.2 硬件組成

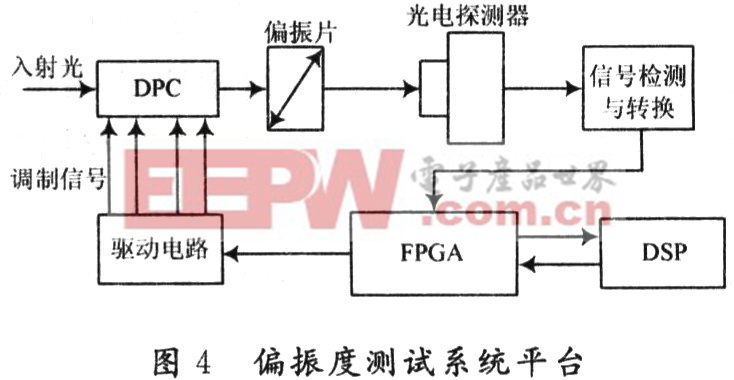

DPC的驅動電路是基于偏振度測試系統平臺(見圖4)研制的。DPC用于將輸入光擾偏后輸出,再經檢偏器和探測器將光強信息轉化為數字量送人FPGA,FPGA對數據進行處理后再對DPC的驅動電壓做出調整并輸出,以達到完全擾偏的目的。

要實現完全擾偏,也即是讓輸入偏振態在一定時間內遍歷各個偏振態。根據DPC的工作原理及實驗嘗試,測試系統使用4路正弦信號同時驅動4個光纖擠壓器。根據DPC自身性質,所需提供電壓最大值應小于2 V,正弦波頻率應小于2 000 Hz。因此,驅動電路需要提供4路大于零的正弦波驅動信號,其峰值應小于2 V。且正弦波頻率各不相等,均小于2 000 Hz。

驅動電路的硬件結構如圖5所示,4路電壓驅動設計均相同。采用16位高精度數/模轉換器LTC1668,將FPGA輸出的數據轉換為模擬電流,再經運放LT1812將電流轉換為電壓。

LTC1668工作在士5 V雙極性電壓供電情況下,其參考電壓由內部提供,輸出采用單端電流輸出模式。寬帶放大器LT1812完成電流一電壓轉換,最終輸出符合要求的正弦信號。

2.3 軟件設計

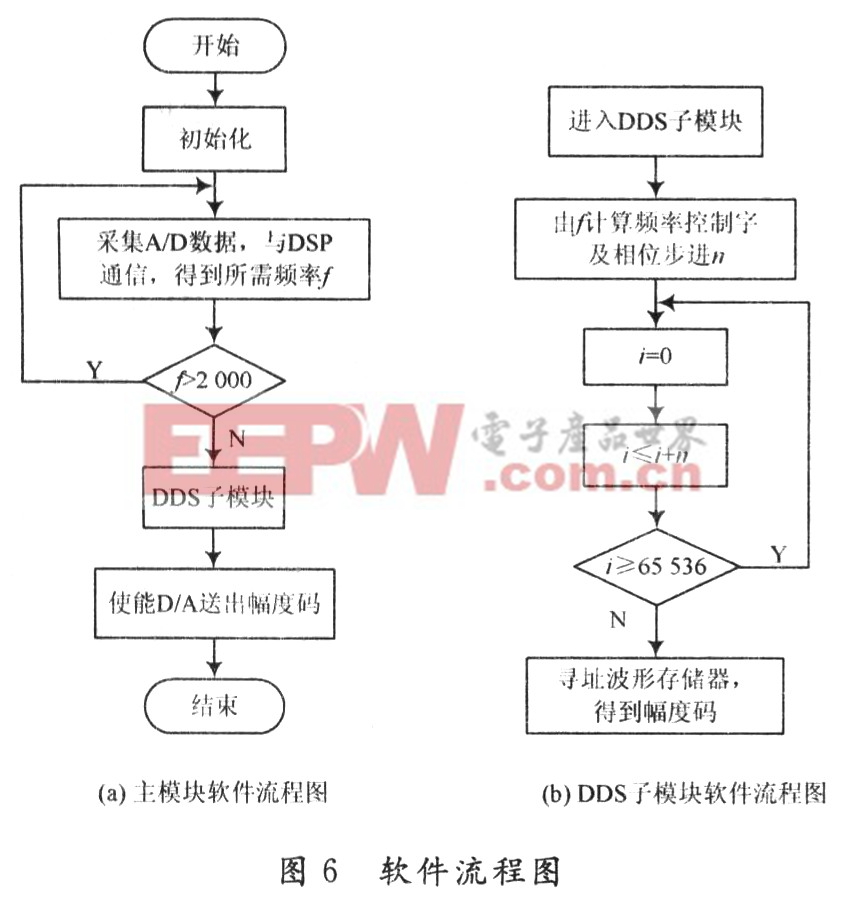

FPGA是驅動電路的控制核心。FPGA接收ADC轉換的光強信息數據,并傳送給DSP;再根據DSP計算所得的數據(即正弦驅動信號的頻率f)判斷是否符合要求,若符合要求則進入DDS子模塊,得到幅度碼并發送給LTC1668,以輸出需要的正弦波。FPGA主模塊流程圖如圖6(a)所示。

式中:fo是輸出頻率;fref為DDS參考時鐘頻率,由FPGA將晶振輸入時鐘經內部鎖相環分頻后產生。

由相位步進累加可得到相位碼,再尋址波形存儲器即可完成相位――幅度轉換,得到相應的幅度碼,輸出給主模塊。由于驅動信號為正弦波,波形存儲器直接調用FPGA內部模塊sin_COS_lookup_table,輸入與輸出數據位寬均為16位。DDS子模塊流程圖如圖6(b)所示。

2.4 實驗測試結果

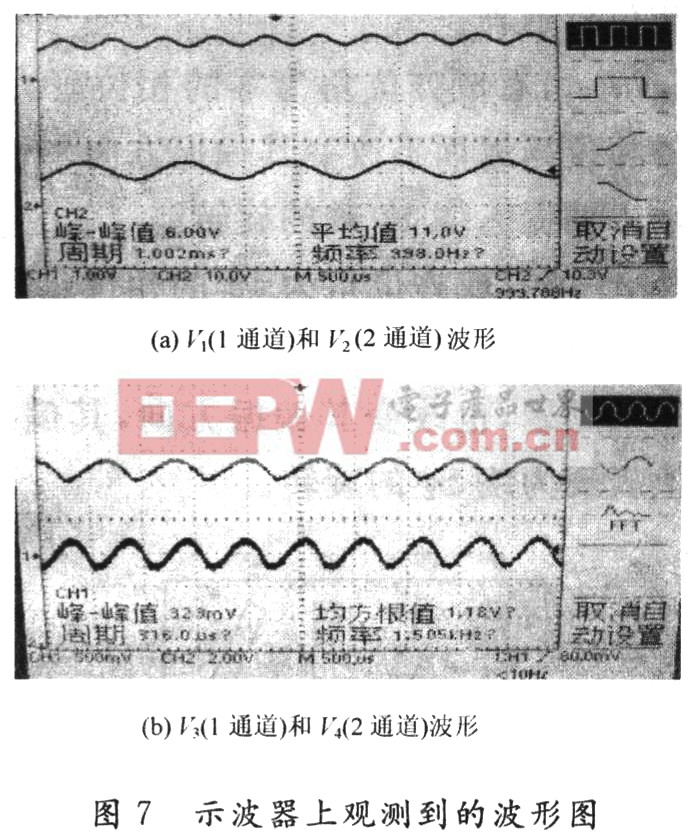

實驗時設定4路正弦驅動信號V1,V2,V3,V4的頻率分別為f1=2 000 Hz,f2=1 000 Hz,f3=1 800 Hz,f4=1 500 Hz。

示波器上觀測的波形如圖7所示。

波形使用雙通道示波器觀測,2通道探頭設置為10檔。從圖7中可以看出,輸出波形較為穩定。如果在FPGA程序內增大sin_COS_lookup_table模塊的輸入數據位寬,也即增大采樣點數,可以得到精度更高的輸出波形。

3 結 語

動態偏振控制器目前廣泛應用于光纖通信和傳感領域,是一種重要的偏振控制器件。分析動態偏振控制器的工作原理,并以光纖擠壓型偏振控制器為研究對象,設計了基于DDS技術和FPGA的調制電路,該設計以偏振度測試系統為實驗平臺。實驗測試結果表明,所設計的調制電路能夠輸出4路頻率可調的正弦信號,輸出信號穩定,控制靈活,工作性能可靠。該方法思路簡單,采用Verilog語言設計并調用FPGA內部模塊,設計靈活透明,且外圍電路較為簡易,具有良好的實用性和性價比。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論