基于FPGA的數字下變頻的研究與實現

(1)由于系數的對稱性,可將有相同濾波系數的輸入數據先進行相加,只用其中4個系數,簡化結構,節約資源。輸人數據為12 b,相加后位寬擴展一位為13 b。

(2)采用全并行的DA結構,每一位數據都有一個深度為24的查找表,將數據每3位分為一組,最后一組為4位,每組查表結果移位相對應位數后相加,結果輸入兩級流水線加法器陣,最后得到濾波輸出值。

(3)設計中應注意的三個問題:

①濾波器系數的量化,把系數擴大2L倍,最后輸出右移L位即可。

②查找表的建立。由于只有4個系數,不用對系數進行分組分別查表以節省查找表資源。

③運算中數據位數的處理,不要溢出。

第二級濾波器的實現跟第一級濾波器類似。本文引用地址:http://cqxgywz.com/article/158029.htm

4 仿真及結果分析

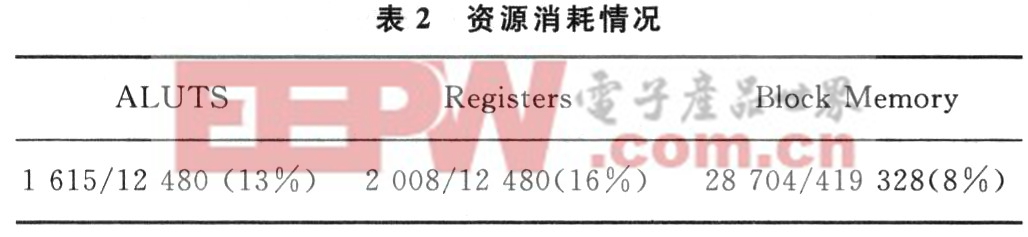

FPGA芯片采用Altera公司的StratixⅡEP2S15F484C3,在QuartusⅡ7.2中布局布線后,資源消耗情況如表2所示。

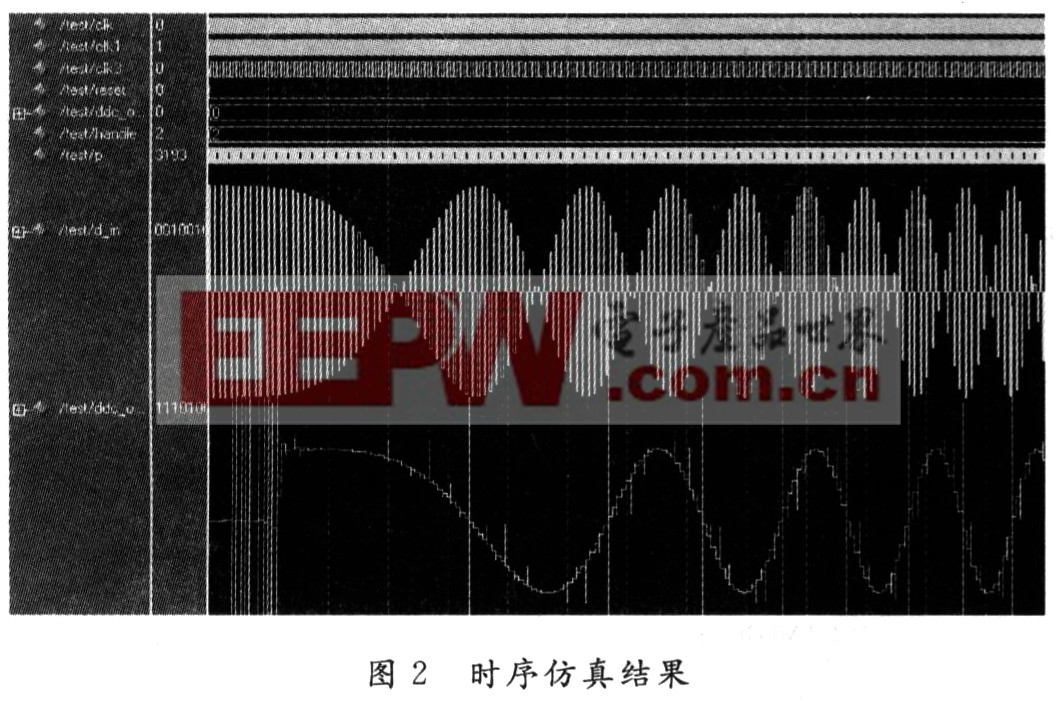

電路最大運行頻率為176.15 MHz,滿足要求。產生一個頻譜帶寬為5 MHz的掃頻信號,將該信號用頻率為70 MHz的余弦信號混頻到中頻處,將其采樣后的值導入ModelSim 6.0中進行仿真,時序仿真結果如圖2所示。

圖2中上方為輸入中頻信號,下方為輸出I路信號。由圖可見,I路得到了原掃頻信號,驗證了設計的正確性。

下面考慮另一種下變頻方案進行比較。如果對相同的信號以60 MHz的速率進行采樣,則NCO的頻率為10 MHz,正余弦樣本值的周期為6,需要用到兩個乘法器進行混頻,設計出的濾波器階數也增加了。布局布線后消耗的FPGA資源超過了前面的設計。

5 結 語

由以上討論可知,選擇合適的采樣率的好處如下:

(1)可以減少NCO的樣本值數,從而減少混頻時的資源消耗;

(2)可以簡化抽取濾波器的設計。

同時,使用基于并行DA算法的濾波器,則可以用較小的硬件資源實現高速率的濾波功能。正是基于以上優點,本文設計的數字下變頻方案以較少的資源完成了信號的數字下變頻,有重要的實用價值。

評論