基于CMOS圖像傳感器的視頻采集系統設計

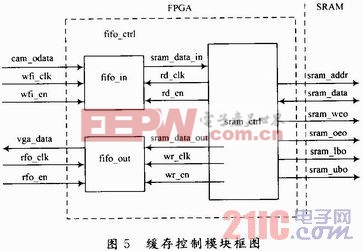

2.4 緩存控制模塊

靜態隨機存儲器(Static Random Access Memory,SRAM)和同步動態隨機存儲器(Synchronous DynamicRandom Access Memory,SDRAM)是目前常用的2種存儲器,2種存儲器各有優劣,而SRAM相對于SDRAM時序控制較為簡單,因此本系統采用SRAM作為數據緩存。緩存控制模塊主要實現將轉換后的數據緩存在SRAM寫FIFO中以及將從SRAM讀出的數據緩存在SRAM讀FIFO中,而前端數據采集和處理是用OV7670輸入的25 MHz的像素時鐘作為主控時鐘的,而SRAM的讀寫時鐘為100 MHz,而后端VGA控制模塊的時鐘也為25 MHz,對于數據在異頻的時鐘域之間的傳輸,需要利用例化2個異步FIFO模塊fifo_in和fifo_out作為數據在不同時鐘域之間的緩沖。FIFO通過IP核實現,存儲寬度為16 b,存儲深度選擇512。緩存控制模塊的框圖如圖5所示。利用FIFO解決異頻時鐘域數據同步的方法是用上級隨路時鐘寫上級數據,然后用本級時鐘讀出數據。由于時鐘頻率不同,因此兩個端口的數據吞吐率不一致,設計時要開好緩沖區,并通過監控確保數據不會溢出。本文引用地址:http://cqxgywz.com/article/159779.htm

2.4.1 fifo_in模塊

在本系統中用數據采集與格式轉換模塊處理后的16位圖像數據作為fifo_in模塊的輸入數據,每次往FIFO中寫一行數據(320個16位數據)OV7670輸入的像素時鐘作為寫時鐘,行有效cam_href作為FIFO寫使能,FIFO的讀時鐘rdclk為100 MHz,也是SRAM的讀寫時鐘。FIFO讀使能產生是通過判斷FIFO寫使能下降沿來生成一個計數值為320的計數器,在計數期間將讀使能置高,將數據由FIFO緩存到SRAM。因為在320個數據寫完后有一段時間行有效為低,由于SRAM讀速率遠大于上一級寫速率,可以充分利用這段時間將數據存入SRAM。

2.4.2 fifo_out模塊

由于采用單片SRAM,SRAM的讀寫要避免沖突。因此通過判斷fifo_out模塊中的wrusedw(FIFO中剩余的數據數量)來控制FIFO的讀/寫。當wrusedw的值小于192時,將一個標志位fifo_empty置高。為避免讀寫沖突,將SRAM讀使能的產生分為2種情況,在幀有效信號置高期間,此時一幀圖像的數據正在由圖像傳感器輸出,SRAM會存在寫入數據的情況,只有在fifo_empty置高和SRAM寫使能下降沿同時滿足的情況下讀使能才會置高,而在幀有效信號為低期間,SRAM不會寫入數據,只需在fifo_empty置高時一個計數值為320的計數器開始計數,在汁數期間將讀使能置高即可。而FIFO的讀使能來自VGA控制模塊,在需要輸出圖像數據到VGA顯示器上顯示時,VGA控制模塊讀FIFO使能置高,來讀取FIFO中的圖像數據。

2.5 VGA控制模塊

VGA(Video Graphics Array)即視頻圖形陣列,是IBM在1987年隨PS/2機一起推出的一種視頻傳輸標準,具有分辨率高、顯示速率快、顏色豐富等優點,在彩色顯示器領域得到了廣泛的應用。

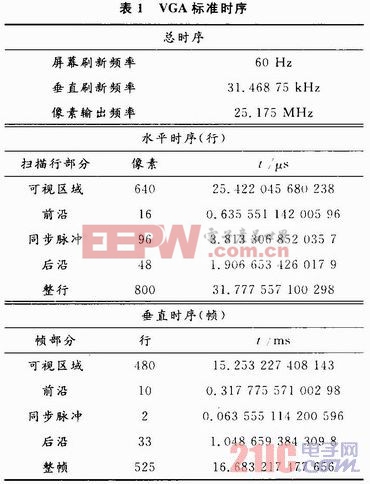

VGA控制模塊主要是產生符合要求的VGA時序,使得視頻圖像數據能夠正確地在VGA顯示器上進行顯示。本系統中VGA控制模塊產生的是分辨率為640×480,刷新率為60 Hz的VGA時序,并將從SRAM讀出的16位像素信號分成5位red信號、6位green信號和5位blue信號,輸出到D/A轉換電路。

VGA控制模塊中主要利用行同步計數器hcnt和場同步計數器vcnt來分別產生行同步和場同步。時序主要參考分辨率為640×480,刷新率為60 Hz的VGA工業標準時序,如表1所示。

評論