新型時鐘日歷芯片DS12C887的應用設計

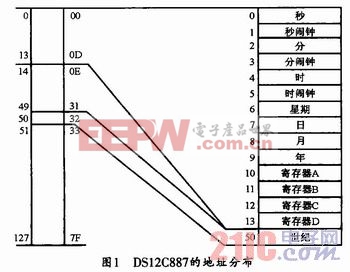

DS12C887實時時鐘日歷芯片的地址分布如圖1所示,芯片內部的所有地址都包括113字節的通用RAM,另外還有11字節RAM用來存儲時間信息,4字節RAM用來存儲控制和狀態信息(稱為控制寄存器)。除以下情況外,所有128字節RAM都可以直接讀寫;

(1)寄存器C和D為只讀;

(2)寄存器A的第7位為只讀;

(3)秒字節的高位為只讀。本文引用地址:http://cqxgywz.com/article/162244.htm

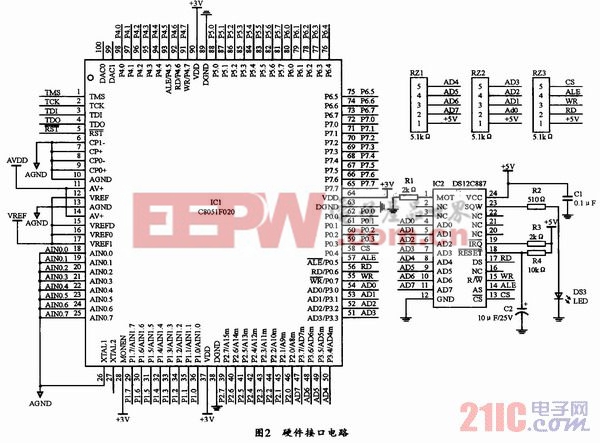

2 硬件接口電路設計

圖2所示為C8051F020與DS12887的硬件接口電路原理圖。圖中,C8051F020選用內部振蕩器,DS12C887芯片的MOT引腳接地,以選用MOTO-ROLA總線時序。本設計把DS12C887的RAM作為C8051F020外部存儲器進行讀寫,因而程序簡單,指令執行時間短。C8051F020外部的存儲器接口可以位于低端口或者高端口,并可通過對外部存儲器接口配置寄存器(EMIOCF)和外部存儲器接口控制寄存器(EMIOCN)進行設置,其中外部存儲器模式應為帶塊選擇的分片方式,并應確定外部存儲器的首地址。如果沒有此功能,最好將片![]() 選接ECU地址總線高字節。對于51單片機來說,一般可將P2口用于控制信號,P0口作為數據通道。

選接ECU地址總線高字節。對于51單片機來說,一般可將P2口用于控制信號,P0口作為數據通道。

存儲器相關文章:存儲器原理

電荷放大器相關文章:電荷放大器原理 電容傳感器相關文章:電容傳感器原理

評論