實時視頻采集系統的SDRAM控制器設計

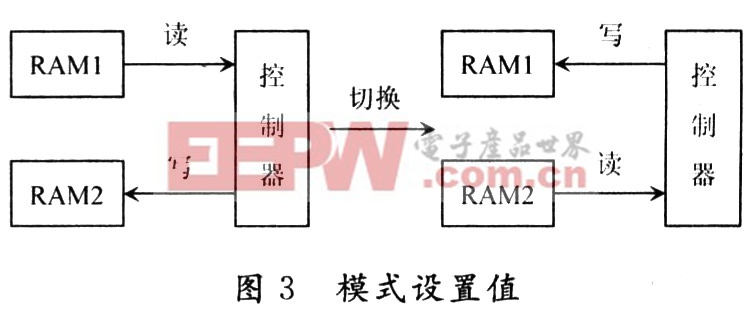

在實時視頻采集系統中,為了保證數據的穩定和連續性,通常采用的方法是對存儲器進行乒乓操作。一般所指的乒乓操作針對兩片存儲器芯片,如圖3所示,其原理是通過控制模塊對兩片存儲器分別做讀寫操作,寫存儲器滿時控制模塊發出交換命令,切換兩片存儲器的操作狀態。本文引用地址:http://cqxgywz.com/article/163469.htm

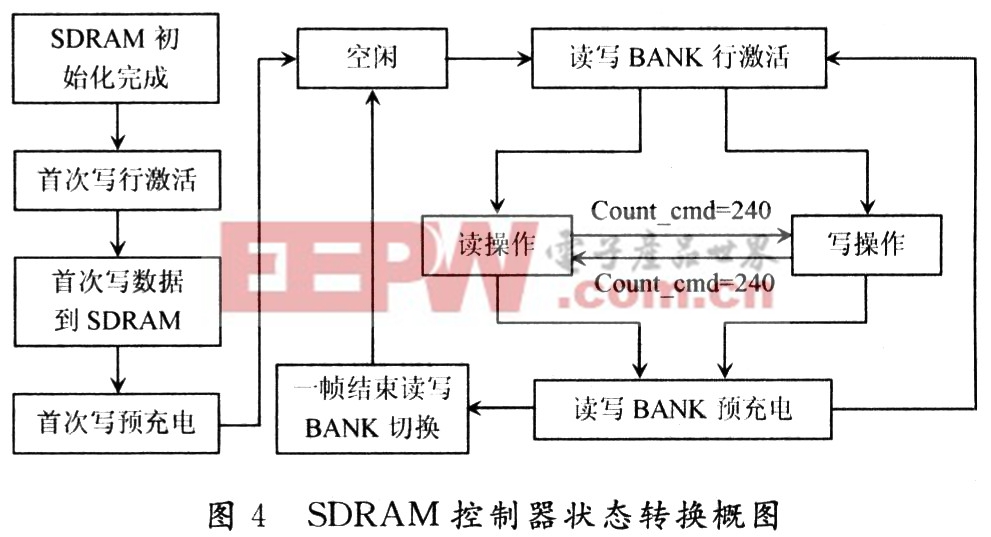

該系統采用的是一片SDRAM實現乒乓操作。設計時是利用SDRAM的不同BANK間的存取操作來實現乒乓操作。由于SDRAM總共有4個BANK,所以讀取第一幀圖像時使用SDRAM的1,2 BANK為讀緩存,3,4 BANK為寫緩存。第二幀圖像時SDRAM的3,4 BANK切換為讀緩存,1,2 BANK切換為寫緩存。采用一幀圖像讀寫完畢作為切換標志反復切換讀寫緩存,就充分利用SDRAM的不同BANK來實現乒乓操作。另一方面由于SDRAM的數據線和地址線只有1組,所以實際控制的時候讀寫操作是不能同時進行的。設計中考慮到SDRAM的工作頻率與前端圖像采集的像素頻率以及后端VGA顯示的像素頻率相比要高得多,因此將讀寫操作利用時分的方式分開控制。所以在控制器中設計了一個指令計數器(Countcmd),通過計數的方式來切換讀寫操作。只要選取適當的SDRAM工作頻率以及指令計數器的規定值就可以完成SDRAM讀寫操作的連續切換。實際設計中采用的SDRAM工作頻率為100 MHz,指令計數器的規定值為240。SDRAM控制器狀態轉換概圖如圖4所示。

SDRAM控制器的具體狀態轉換流程如下:首先初始化SDRAM,然后向SDRAM的1,2 BANK寫入第一幀圖像,當第一幀圖像寫入完畢后進入乒乓操作階段。此時SDRAM的1,2 BANK為讀緩存,3,4 BANK為寫緩存。

首先進入讀緩存激活行,開始讀操作,讀操作開始的同時啟動指令計數器。此時每執行一條指令(包括讀指令,空操作指令,不包括預充電指令和行激活指令),指令計數器自加1,當指令計數器到達規定值時將指令計數器清0并切換到寫狀態。進入寫狀態前先判斷寫緩存的行激活標志,如果沒有激活,先執行行激活,然后開始寫操作,如果已經激活則直接開始寫操作。寫操作開始的同時啟動指令計數器。此時和讀狀態時一樣,每執行一條指令,指令計數器自加1,當指令計數器到達規定值時同樣將指令計數器清0后切換到讀狀態。如此反復切換操作,直至讀完一幀或者寫滿一幀。如果是讀完一幀,則判斷寫緩存中一幀寫滿沒有。如果已經寫滿,則進入讀寫BANK切換狀態。如果沒有,則進入寫狀態并不再切換讀寫狀態,一直保持寫狀態直至寫滿一幀為止,然后進入讀寫BANK切換狀態。如果是寫滿一幀,則同理于讀完一幀的情況,首先判斷讀緩存中讀完一幀沒有,然后根據判斷結果進行操作,最后進入讀寫BANK切換狀態。在讀寫BANK切換狀態中,讀緩存切換為3,4 BANK,寫緩存切換為1,2 BANK。反復上述操作步驟,就可以完成使用一片SDRAM不同BANK的乒乓操作。整個SDRAM控制器在Altera的QuartusⅡ7.2環境下采用Verilog設計完成,然后在ModelSim SE 6.0環境下仿真通過。隨后通過Altera的QuartusⅡ7.2進行綜合和布局布線,并最終在Al-teraCyclone系列FPGA芯片EP1C6Q240C8上完成。所設計的SDRAM控制器在PAL→VGA的實時視頻采集系統中調試通過,能夠實現圖像數據的存儲和讀取,完全滿足系統的要求。

3 結 語

介紹在PAL→VGA的實時視頻采集系統中使用SDRAM作為圖像緩存的基本操作,設計一種使用1片SDRAM的不同BANK進行乒乓操作的相對容易實現的SDRAM控制器設計方法。在PAL→VGA的實時視頻采集系統中,使用了所設計的SDRAM控制器,并通過硬件驗證,采集得到的圖像質量較好。另外,這里設計的SDRAM控制器稍加改動就可以應用到其他實時視頻采集系統中去,具有很強的通用性。

pid控制器相關文章:pid控制器原理

評論