基于DSP的運動控制器的研究與開發

摘要: 由于DSP將超強的高速實時處理能力和豐富的外設功能集于一身,目前,以DSP為核心的嵌入式運動控制器已經成為開放式運動控制器的發展主流,并獲得廣泛的應用。本文通過 對運動控制器基本功能的研究,在分析、消化已有的基于DSP的運動控制器硬件資源基礎上,開發了運動控制器的軟件系統,詳細介紹了運動控制器的軟件設計。

本文引用地址:http://cqxgywz.com/article/163936.htm關鍵字: 軟件開發;DSP;運動控制

1 運動控制器硬件結構

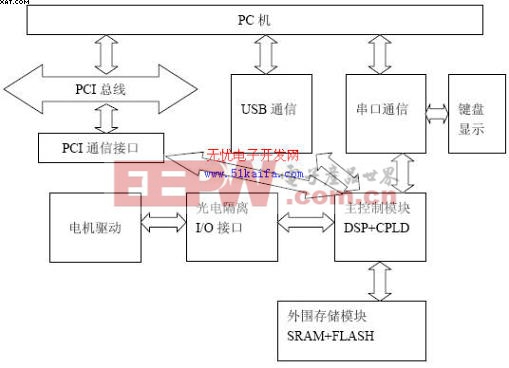

本運動控制器的硬件結構主要分為如下幾個模塊:DSP+CPLD 主控模塊,包括 DSP 核心 模塊和 CPLD 驅動與擴展模塊;通信接口模塊,包括 PCI 總線、USB 總線和串口;I/O 輸入輸 出接口模塊以及外圍存儲器模塊,包括 SRAM 和 FLASH。本運動控制器的硬件結構如圖 1 所示。

圖 1 運動控制器硬件結構圖

1.1 DSP+CPLD 主控模塊

本系統采用了 TI 公司的 TMS320F2812 DSP 為控制核心,這是工業界首批 32 位的控制 專用、內含 FLASH 以及高達 150MHz 主頻的數字信號處理器,專門為工業自動化、光學網絡及自動化控制等應用而設計的。TMS320F2812 采用哈佛總線結構,有獨立的程序和數據空間;具有很強的運算能力,能夠實時地處理許多復雜的控制算法;片上內存豐富,可支持45 個外設級中斷和 3 個外部中斷,提取中斷向量和保存現場只需 9 個時鐘周期,響應迅速; 片上集成了多種先進的外設,包括兩個事件管理器(EV)、12 位 A/D、兩個串行通信接口(SCI)、一個串行外圍接口(SPI)以及一個多通道緩沖串行接口(McBSP)等;其通用輸 入/輸出多路復用器(GPIO)擁有多達 56 個 I/O 口,在系統的軟件開發中正是利用了這些豐富的內外設資源,才實現了系統要求的各種功能。

本系統中選用的 CPLD 是 Altera 公司 MAX3000A 系列的 EPM3128,這是一款高性能、 低功耗的基于 EEPROM 的 PLD。由于本系統的控制對象是步進電機,所以設計中主要利用TMS320F2812 的 GPIO 口進行電機控制接口與 I/O 接口的輸入輸出,但是由于 TMS320F2812

是低功耗處理器,其 GPIO 引腳的輸出驅動能力有限,而且由于 DSP 是主控核心,負載比 較多,所以將所有輸出信號都經過 CPLD 驅動后輸出,提高信號的驅動能力。此外,CPLD還用于系統電路的譯碼,增加系統設計的靈活性和可擴展性。

1.2 通信接口模塊

本系統在用作插卡式運動控制時利用 PCI 總線實現 DSP 與 PC 的通信。PCI(PeripheralComponent Interconnect 外圍部件互聯)總線是 Intel 公司聯合其他 100 多家公司于 1992 年推 出的基于新一代處理器的一種局部總線,是一種高性能 32/64 位數據/地址復用總線,能為 CPU 及外設提供高性能數據。PCI 總線具有嚴格的規范,目前已經發布了 PCI V1.0 和 V2.1規范,保證了其良好的兼容性;PCI 總線與 CPU 無關,與時鐘頻率也無關,可適用于各種平臺,支持多處理器和并發工作;PCI 總線可以提供極高的數據傳輸速率,還具有良好的擴 展性。因此,PCI 總線在基于計算機總線的運動控制系統,即“PC+運動控制器”的結構中應用十分廣泛。

本系統選用 CYPRESS 公司的 CY7C68001 芯片實現 PC 機和 DSP 之間的 USB 通信。CY7C68001 是通用 USB2.0 接口控制器,它是基于應用層編程的接口器件,相對于其它基于 鏈路層編程的接口器件,使用和開發都很方便。本系統采用 DSP 片上的 SCI 串行通信模塊以及 MAX232 芯片轉換成標準 RS-232 的通 信信號,實現正常的串口通信。

1.3 I/O 輸入輸出接口模塊

本系統的輸入/輸出是通過 CPLD 的邏輯控制來實現的,以提高系統的工作可靠性和設 計柔性。考慮到運動控制器的可擴展性以及 DSP 的 GPIO 引腳的數量,共設計了 16 路數字量輸出通道和 16 路數字量輸入通道。數字量輸出通道主要用于各軸方向、脈沖信號的輸出以及一些外部設備的啟停控制,如主軸及冷卻液的開關控制等;數字量輸入通道可根據用戶 具體要求來定義其用途,如作為傳感器接口,用于零點、限位信號的輸入等。為提高系統應用的靈活性,系統輸出采用了普通輸出和差分輸出兩種方式,具體使用可由用戶自行設定。

1.4 外圍存儲器模塊

TMS320F2812 芯片內部包括 128KB 的 FLASH 和 18KB 的 SARAM,其中 128KB 的

FLASH 用來存儲系統軟件程序已經足夠,但是在實際使用中,考慮到運動控制指令和加工程序需要通過 USB 總線或 PCI 總線下載到運動控制器中,且 DSP 在工作過程中需要處理大 量的數據,僅依靠 DSP 芯片內部的存儲空間遠遠不夠,所以考慮外擴一片 FLASH 和一片SRAM 作為用戶加工程序存儲器和系統的工作存儲器,它們通過 CPLD 完成與 DSP 之間的讀寫操作。

本系統選用了 Intel 公司的 E28F128 FLASH 和 ISSI 公司的 IS61LV51216SRAM。E28F128 是一種采用 CMOS 工藝制成的 8MB 的 FLASH,其讀寫訪問時間為 150ns,此讀寫周期已經 大于 DSP 對外部端口的讀寫周期,為了能夠和 DSP 的讀寫周期進行匹配,在對 FLASH 進 行讀寫操作過程中必須插入等待周期。IS61LV51216 是一種高速異步靜態 512KB 的 SRAM, 其讀寫周期為 10ns,與 DSP 之間可以無需插入等待周期便可以進行讀寫操作,并可以直接映射到 DSP 外部存儲接口的 Zone2 或者 Zone6 區域。

2 運動控制器軟件結構

評論