基于LPC2210的LED顯示屏控制系統設計

在設計中,采用LPC2210P0口的16個引腳作為顯示控制電路的接口,并分別對應屏的使能端EN、行選中信號端(A,B,C,D)、行點亮數據信號端(GD1,GD2,RD1,RD2)和2路時序信號LAT,CLK等。本文引用地址:http://cqxgywz.com/article/169346.htm

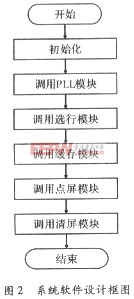

2 系統軟件設計

由于本LED顯示屏的顯示控制電路,主要采用74HCl38和74HC595完成行掃描,以控制時序的方式完成列控制,且這些時序是由軟件部分完成的,因此在軟件系統的設計中,首要考慮時序邏輯的合理設計與實現。在本LED顯示屏中,需要2路時序分別是完成數據緩存的緩存時序CLK及將緩存數據點亮的點屏時序:LAT。CLK出現上升沿后,將數據依次存入屏的緩存,LAT出現上升沿后,屏將緩存內容送到屏的某一行。除此之外還要考慮行掃描過程中行的選擇以及顯示模塊、通信模塊、清屏模塊等,子模塊的編寫與各子模塊間的協調使用等問題。

需要指出的是為了提高LED顯示屏的可擴展性,就勢必使系統提高了對頻率的要求,為此本設計在系統軟件的設計過程中,利用LPC2210微處理器自帶的鎖相環(PLL),對系統進行了倍頻設計,以提高系統的可擴展性。系統軟件架構設計,如圖2所示。

2.1 PLL模塊

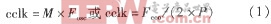

LPC2210的PLI接收的輸入時鐘頻率范圍是10~25 MHz,選用11.059 2 MHz作為系統的外部晶振頻率,首先需要配置PLL,計算公式如式(1)所示。

其中,Fosc為晶振頻率,Fcco為PLL電流控制振蕩器的頻率,cclk為PLL的輸出頻率即處理器的時鐘頻率,M與P分別為PLL的倍增器值與分頻器值。

CCO頻率可由式(2)得到。

![]()

評論