兼容51指令的8位MCU IPCORE設計

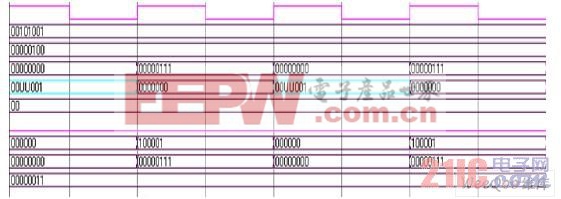

利用Mentor Graphics 的工具MODELSIM SE/對模型進行了模擬驗證。此處僅給出了一個簡單的指令執行后的模擬結果(見圖4)。圖中所示為ADD A RN指令的波形圖,可以看出,模擬結果與指令執行結果一致。該模型也通過了MODELSIM的可綜合性檢查。

圖4 指令ADD A RN 執行結果

5.2 時序測試

在時序測試中我們選用了ALTERA 公司的不同系列FPGA 芯片來對次IPCORE 進行綜合,綜合后的性能如下表所示:

從上表我們可以看出雖然不同的器件綜合后的結果不相同,但是本文設計的8 位MCUIPCORE 可以完全可以容納到一個相對門數為20 萬門以上的FPGA 中,并且具有較好的時鐘頻率特性。

6 結論

雖然這里只設計了一款八位的MCU IP CORE,但我們所提出的架構和模塊設計新思路可以推廣到16位、32位以及64位MCU的設計中。因為不管是多少位的MCU CORE,設計中需要重點考慮的架構以及指令系統基本上是一致的,所不同的只是一些總線位數以及寄存器的位數而已。當然隨著位數的增加,一些驗證和測試的復雜度也將顯著增加,但從設計思路的角度來講,它們是一樣的。在具體的推廣中,要根據應用領域的不同,對這些方法進行適當的取舍或適當的改進,以更加符合某些具體應用領域的要求。

本文創新點:本文設計了一種新結構的兼容51指令的MCU IPCORE。設計中引入了純組合的ALU單元,增加了并行乘除法器,重新設計了外圍組件,在設計控制單元的時候,重新設計了指令的時序,并且把指令狀態機的時序和組合部分分開設計,提高了狀態機的執行效率。從結果上看,時鐘頻率提高了很多,可由用戶根據需要選擇合適的ROM和RAM 的大小,并且完全可以把此核放在一個相對門數在20萬門以上的FPGA的中。

評論