CDMA 2000系統中前向鏈路卷積編碼器的FPGA實現

2 CDMA 2000系統中前向鏈路卷積編碼器的實現

2.1 CDMA 2000前向鏈路卷積編碼器的電路組成

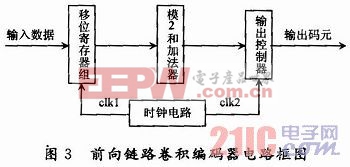

該設計采用模塊化的設計方法,根據CDMA2000系統中的前向鏈路卷積編碼器的功能將其內部結構分為:移位寄存器組、模2和加法器、輸出控制器以及時鐘電路等四個模塊,每一模塊對應一部分VHDL的設計文件,這樣利于程序的編寫和調試,從而降低了整個程序的調試難度,提高了軟件的可維護性和可讀性。前向鏈路卷積編碼器的組成框圖如圖3所示。本文引用地址:http://cqxgywz.com/article/172582.htm

其中,時鐘信號clk1和clk2可由基站控制器(BSC)的時鐘電路直接提供,或由本次設計的時鐘電路將基站控制器(BSC)提供的原始時鐘信號進行分頻得到;輸出控制器包括輸出數據合成電路和整形電路兩部分。

2.2 CDMA 2000前向鏈路卷積編碼器的仿真實現

根據卷積編碼器電路框圖,采用VHDL語言編寫前向鏈路卷積編碼器的源程序輸入到QuartusⅡ開發軟件中進行編譯、仿真、綜合得到可下載文件,然后通過對器件編程完成設計。

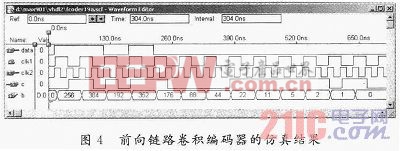

仿真前假設編碼器的初始狀態為零,即:b1~b9為00000000;輸入的信息為11010,為保證輸入的全部信息位都能通過移位寄存器,并對移位寄存器進行復位,在信息位后加8個零,其輸出結果為11010111000001111111101100,,仿真時,輸入數據data的速率為9.6Kb/s;輸出碼元c的速率為19.2Kb/s。仿真結果如圖4所示,其中b為寄存器組各個時刻的狀態。

在前向鏈路卷積編碼器的設計中有一些需要注意的問題:首先要明確VHDL語言不同于其他的計算機語言,它是一種硬件描述語言,它描述的對象是客觀的電路系統。其次,不同的EDA工具對VHDL語言的支持程度不同。本次設計中采用的QuartusⅡ開發工具主要是針對可編程邏輯器件的軟件,它并不支持所有的VHDL語句,它只支持RTL級描述,不支持行為級描述。再有,在設計中需要根據設計要求和可編程邏輯器件的資源情況、速度等進行合理的選擇。該設計中采用的EP2C8Q208器件就可滿足資源和速度方面的要求。

3 結語

本文實現了一種適用于CDMA 2000系統的前向鏈路卷積編碼器,通過對整體電路的設計、仿真和調測,結果表明本編碼器可達到CDMA 2000系統要求,具有一定的實用價值,同時,本設計采用基于可編程邏輯器件借助VHDL語言及EDA工具進行設計的思路,大大縮短了設計周期,降低了成本,提高了設計的可靠性、靈活性,為通信系統設計提供了一種有效的設計方法。

評論