基于80C196KC的ARINC429總線接口板設計

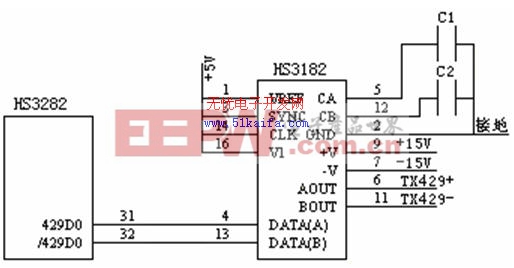

HS-3182是作為ARINC429總線的發送設備完成兩路信號的差分驅動,與HS-3182相連的電容控制用來控制ARINC429的傳輸速率,其中c1,c2為75pF時對應ARINC429總線的高速狀(100Kbps)、為300pF時對應ARINC總線的低速狀態(12.5Kbps),因此盡量用高精度、軍品級的電容,HS-3282和HS-3182相連的電路圖如圖2所示:

圖2 HS-3282和HS-3182的連接圖

3.2 ARINC429總線收發硬件電路

硬件的計算機系統采用Intel的16位單片機80C196KC,該CPU可以動態的配置成8位或者16位的總線寬度,結構采用寄存器結構,有232字節的RAM寄存器陣列供用戶配置,外接晶振為12MHz或者20MHz,可以滿足ARINC429總線的高速發送和接收。CPU和HS-3282的接口比較簡單,發送時常和HS-3182相配合使用,因為HS-3282的數據寬度為16位的,因此單片機也配置成16位總線寬度,CPU和HS-3282的接口部分關鍵就是對收發的邏輯控制,諸如接收器1數據可以讀取標志D/R1,接收器2數據可以讀取標志D/R2,總線選擇信號SEL等端口都需要CPU的控制和監視,在這里就直接和CPU的I/O口相連,當然也可以通過CPU的I/O,/RD,/WR及地址的低位和GAL或者CPLD相連,通過編成組成專門的邏輯控制電路,這在單片機的I/O口不夠用時可以采用這種辦法,HS-3282需要CPU控制和監視的管腳如表3所示:

表3. S-3282控制及狀態的引腳及功能

由于HS-3282是外圍器件,收發速率都沒有CPU快,因此要為CPU提供READY信號,在這里為CPU提供READY信號的是/EN1和/EN2管腳,只要這兩個管腳有一個是低電平就可以產生READY,因此對這兩個信號加一個與非門既可以產生READY信號。

4 軟件設計

HS3282的收發既可以采用查詢方式又可以采用中斷方式,由于發送器狀態標志位TX/R接到CPU的I/O口,這就限制了軟件設計時發送采用查詢方式。接收兩種方式都可以,在這里采用中斷方式接收。

初始化程序設計

在上電復位后單片機應首先進行自身初始化和HS3282的設置,主要是設置單片機的波特率和向HS3282寫控制字。在這里設置單片機的串口為工作模式1,即10位構成一串行幀: 1位起始位(0),8位數據(低位在先),1位停止位(1)。單片機首先將控制字寫到P3和P4端口,通過置高再置低P2.7端口,將控制字在/CWSTR的下降沿寫入,進行工作方式、碼速率等的設置。

接收程序設計

數據的接收以中斷響應的處理為核心。HS3282有兩路接收通道,這兩個接收通道標志位/DR1、/DR2共享一個中斷,就容易出現中斷沖突現象,為了避免這種現象在硬件設計中已經考慮到了這種問題,將接收器標志/DR1、/DR2分別與單片機I/O口的P0.0和P0.1相連接,當產生接收中斷時,通過軟件檢測方式判斷是哪一路引起的中斷,其軟件設計如下:

ReceiverData(char *data)

{

if(P0.0==0) //P0.0=/DR1

{ P1.3=0; //P1.3=SEL

P1.4=0; //P1.4=/EN1

*data=P3;

*(data+1)=P4; //接收低16位

P1.3=0;

P1.4=1;

P1.4=0;

*(data+2)=P3;

*(data+3)=P4; //接收高16位

}

else

if(P0.1==0) //P0.1=/DR2

{ P1.3=0;

P1.5=0;

*data=P3;

*(data+1)=P4; //接收低16位

P1.3=0;

P1.5=1;

P1.5=0;

*(data+2)=P3;

*(data+3)=P4; //接收高16位

}

}

發送程序設計

評論