電源噪聲的危害性分析

芯片發展的一個大趨勢就是集成度越來越高,內部晶體管數量越來越大。芯片的外部引腳數量有限,為每一個晶體管提供單獨的供電引腳是不現實的。芯片的外部電源引腳提供給內部晶體管一個公共的供電節點,因此內部晶體管狀態的轉換必然引起電源噪聲在芯片內部的傳遞。

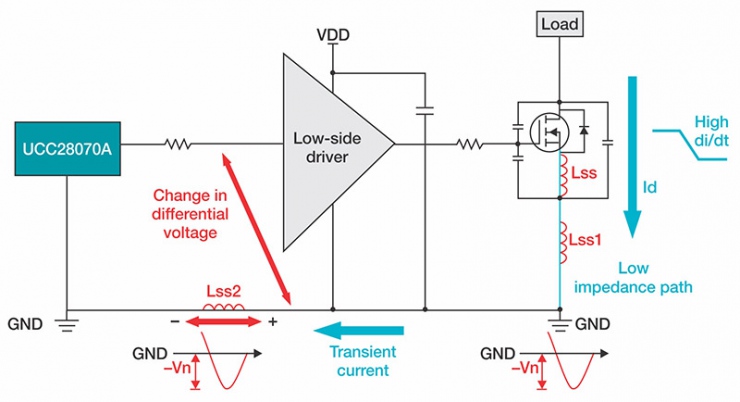

本文引用地址:http://cqxgywz.com/article/175674.htm對內部各個晶體管的操作通常由內核時鐘或片內外設時鐘同步,但是由于內部延時的差別,各個晶體管的狀態轉換不可能是嚴格同步的,當某些晶體管已經完成了狀態轉換,另一些晶體管可能仍處于轉換過程中。芯片內部處于高電平的門電路會把電源噪聲傳遞到其他門電路的輸入部分。如果接受電源噪聲的門電路此時處于電平轉換的不定態區域,那么電源噪聲可能會被放大,并在門電路的輸出端產生矩形脈沖干擾,進而引起電路的邏輯錯誤。芯片外部電源引腳處的噪聲通過內部門電路的傳播,還可能會觸發內部寄存器產生狀態轉換。

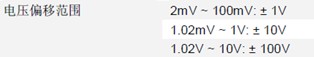

除了對芯片本身工作狀態產生影響外,電源噪聲還會對其他部分產生影響。比如電源噪聲會影響晶振、PLL、DLL的抖動特性,AD轉換電路的轉換精度等。

由于最終產品工作溫度的變化以及生產過程中產生的不一致性,如果是由于電源系統產生的問題,電路將非常難調試,因此最好在電路設計之初就遵循某種成熟的設計規則,使電源系統更加穩健。

評論