低成本多路輸出CMOS帶隙基準電壓源設計

2.2 啟動電路

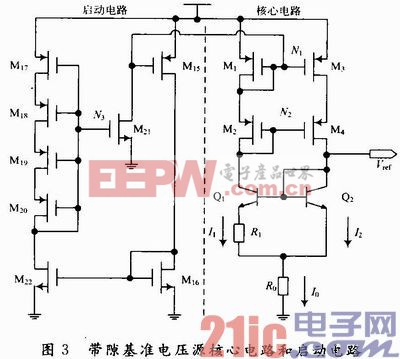

由于本文所設計的帶隙基準源采用的是自偏置結構,因此需要增加啟動電路使帶隙主電路擺脫簡并偏置點。圖3虛線右側所示,電路未啟動時,N1和N2始終保持高電位,輸出則保持在零狀態,并且一直處于這種狀態。啟動電路的作用就是使電路擺脫這種零狀態,進入正常工作狀態。本文引用地址:http://cqxgywz.com/article/175844.htm

本文所設計的啟動電路如圖3虛線左側所示,在電路啟動時,N3變為高電位使M21導通,則N1變為低電位使M15導通,并且帶隙主電路開始工作,啟動完成。由于M16為二極管接法,所以M16支路導通,并且M22與其所在支路也導通了,此時M22的導通將N3拉到較低電位,使M21截止,并且由于M22所在支路的導通,會使M21一直保持截止狀態,啟動電路停止工作,降低了功耗。

2.3 多路基準電壓輸出的設計

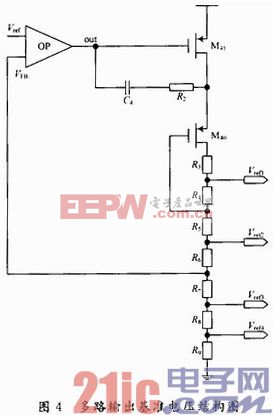

多路輸出電路如圖4所示,整個電路相當于一個帶負反饋的多輸出放大器,可以得到穩定的3 V,2 V,1 V和0.15 V基準電壓。由于Vref為1.14 V,利用運放的“虛短”可得到Vref1,Vref2,Vref3和Vref4的值,其中Vref2計算式為:

![]()

評論