新型高線性折疊結構混頻器設計

2 電路仿真

該混頻器設計基于SM IC 0. 18 μm標準CMOS工藝,用Advanced Design SySTem軟件進行電路設計與仿真。電源電壓1. 2 V; RF頻率為2. 5 GHz,功率為- 30 dbm; LO頻率為2. 6 GHz,本振信號的電壓擺幅VLO = 600 m Vpp。

圖3是三階交調點( IIP3)隨本振功率變化曲線,在本振功率為0 dBm時, IIP3達到最大值3. 857dBm。當本振功率大于或小于0 dBm時, IIP3都會急劇下降。圖4是噪聲系數(NF)和轉換增益(Con2version Gain)隨本振功率變化曲線,本振功率為- 3dBm時,噪聲系數達最小值4. 982 dB,本振功率為- 5 dBm時,轉換增益達到最大值11. 23 dB。考慮到混頻器的整體性能,必須采取折衷,所以選擇本振功率為0 dBm,此時,噪聲系數為5. 257 dB,轉換增益為9. 787 dB。圖5是當本振功率為0 dBm時,噪聲系數隨輸出頻率變化曲線,噪聲系數隨著輸出頻率的增加不斷減小,在輸出頻率為100 MHz時,噪聲系數為5. 257 dB。

圖3 IIP3隨本振功率變化曲線。

圖4 NF與轉換增益隨本振功率變化曲線。

圖5 NF隨輸出頻率變化曲線。

圖6是該折疊混頻器的版圖,該版圖用CadenceVirtuoso Layout editor進行設計及優化。RF輸入端的匹配網絡與IF輸出端的buffer都集成在了片內,版圖面積556μm ×966μm。

圖6 折疊混頻器版圖。

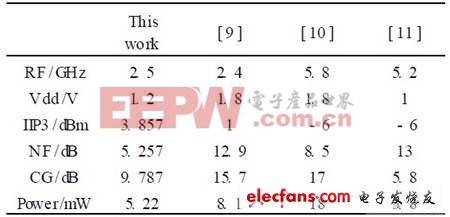

表1是本文設計的折疊混頻器整體性能的仿真結果,并與其他發表的論文做了比較,可以看出該混頻器具有高線性度,低噪聲的優點。

表1 混頻器性能總結與比較

3 總結

本文采用交流耦合互補跨導級成功設計了一種適用于低電源電壓下工作的折疊混頻器。仿真結果表明,該混頻器具有高線性度、低噪聲的優點。

評論