基于可編程計數器的時序邏輯電路設計

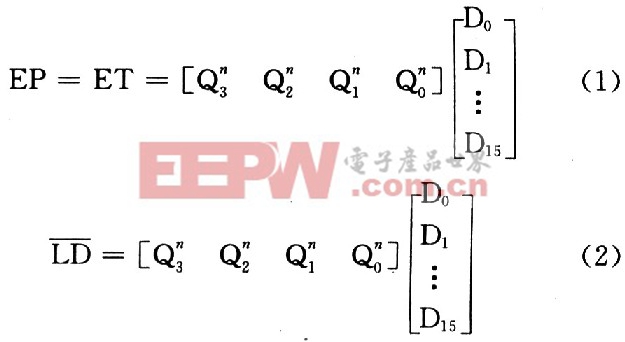

74LS161可編程計數器處于不同現態(tài)時通過數據選擇器選擇不同的外部輸入信號作用于EP,ET及

74LS161可編程計數器的EP,ET及

如果所實現的時序邏輯電路其狀態(tài)個數不超過8個,可使用74LSl61可編程計數器的低3位和2個8選1數據選擇器進行組合。

如果所實現的時序邏輯電路其狀態(tài)個數不超過4個,可使用74LSl61可編程計數器的低2位和2個4選1數據選擇器進行組合。

由狀態(tài)轉換關系,依表2確定式(1),式(2)中輸入矩陣的參數。

1.3 時序邏輯電路的輸出函數

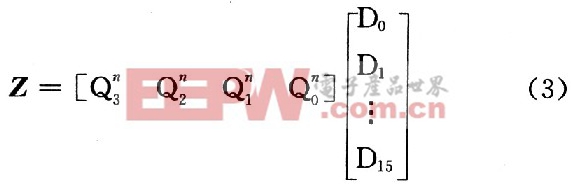

所設計的時序邏輯電路為Mealy型時,輸出是現態(tài)及輸入變量的函數,可寫成式(3)所示的矩陣形式并用數據選擇器實現,由各狀態(tài)的輸出要求確定式(3)中輸入矩陣的參數。

所設計的時序邏輯電路為Moore型時,輸出僅是現態(tài)的函數:

用卡諾圖化簡求出最簡輸出邏輯表達式,用邏輯門實現。

當每態(tài)對應一個不同的輸出函數時,可用二進制譯碼器實現輸出函數。

1.4 基于可編程計數器時序邏輯電路的設計

一般設計步驟:

(1)作出狀態(tài)圖

使用MSI可編程計數器及數據選擇器設計時序邏輯電路時,狀態(tài)的簡化通常不會簡化電路結構,一般不進行狀態(tài)簡化,直接使用原始狀態(tài)圖進行設計,可使各個狀態(tài)所表示的含義清楚,電路與所實現的邏輯功能之間的對應關系較為明確。

(2)狀態(tài)分配

進行狀態(tài)分配時,盡量使用不需進行預置數的二進制時序,盡量對非二進制時序作相鄰分配,以利于預置數的簡化。

(3)求出EP,ET及

(4)畫出邏輯圖。

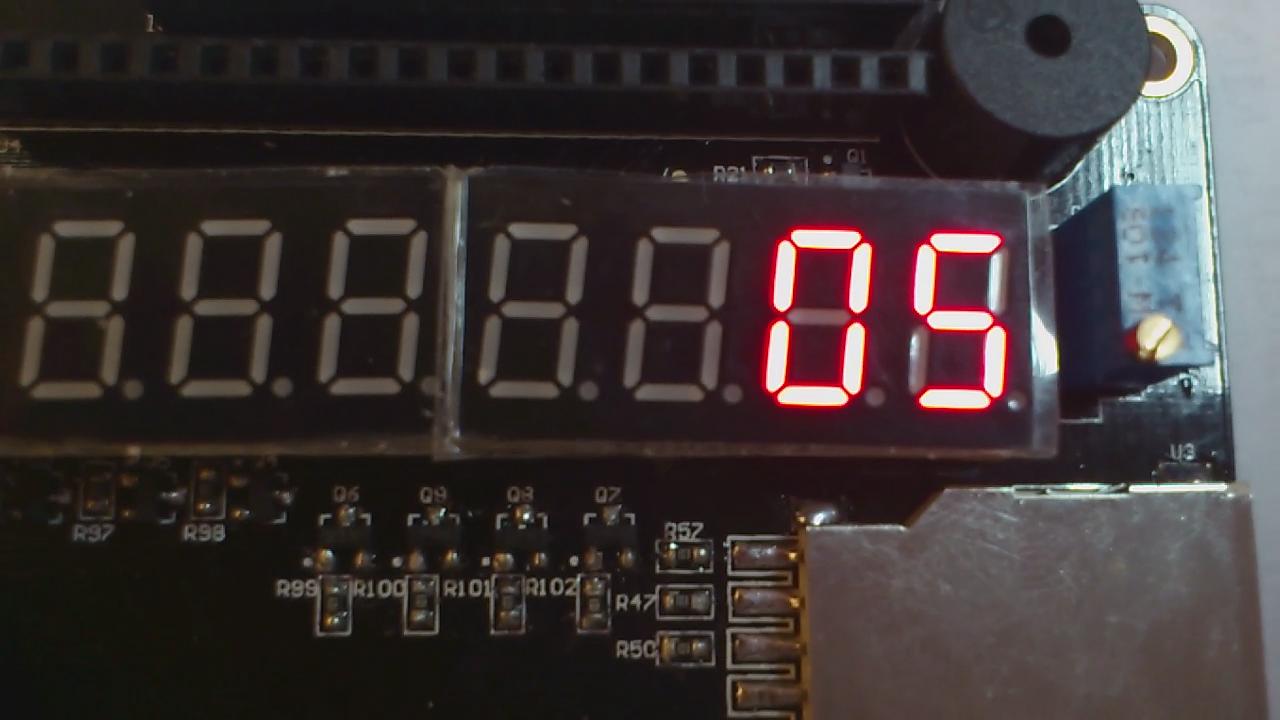

2 設計舉例

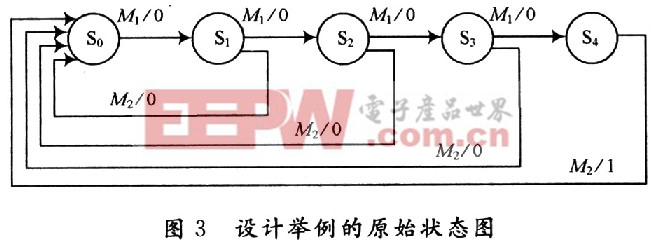

一個同步時序邏輯電路,輸入信號為M1,M2。當M1連續(xù)輸入4個或4個以上的1時,然后M2輸入1個1時,輸出Z為1,M1,M2不同時輸入1。本文引用地址:http://cqxgywz.com/article/180632.htm

由設計要求作出原始狀態(tài)圖如圖3所示。其中,S0狀態(tài)表示起始;S1狀態(tài)表示M1輸入了1個1;S2狀態(tài)表示M1輸入了2個1;S3狀態(tài)表示M1輸入了3個1;S4狀態(tài)表示M1輸入了4個或4個以上的1。

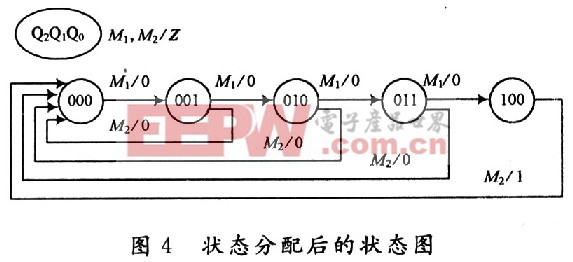

圖3中有S0~S4共5個狀態(tài),使用74LSl61可編程計數器的低3位代碼進行狀態(tài)分配,按盡量使用二進制時序的分配原則,狀態(tài)分配關系為:S0:000;S1:001;S2:010;S3:011;S4:100。

狀態(tài)分配后的狀態(tài)圖如圖4所示。

評論