一種新穎的限流比較器的設計

![]() (9)

(9)

所以, V 2 A 表達式如下:

![]() (10)

(10)

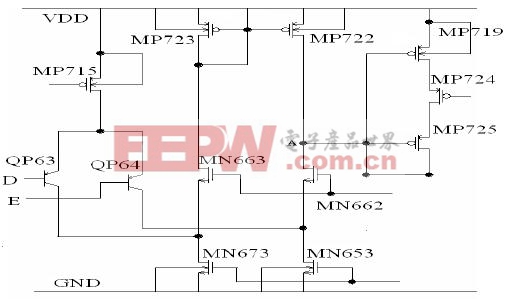

圖2 比較器中間級

3.3 比較器輸出級

比較器的輸出級(Active Load inverter)由A 輸入,B 輸出(圖3),進一步提高放大器的增益,

![]() (11)

(11)

因此,放大器總的增益AV 表達式如下:

![]() (12)

(12)

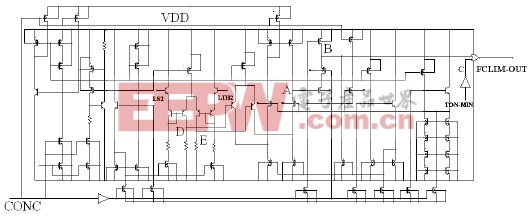

圖3 PFM 限流比較器電路圖

3.4 PFM 限流比較器電路圖

綜合前面比較器輸入級,輸出級,中間級的設計,可得出圖3 所示的PFM 限流比較器電路圖。當功率管導通時,對電感電流充電,使得電感電流上升,同時功率管的漏端電壓下降,電流采樣電路通過采樣導通功率管的漏端電壓,把采樣得到的電壓LS2,LTH2 輸入到PFM 限流比較器,當功率管的漏端電壓下降到一定程度,使得LS2 達到PFM 限流比較器門限LTH2 時,比較器輸出高電平至控制邏輯模塊,從而使芯片進入PFM 工作模式以延長電池壽命。

4 PFM 限流比較器的仿真

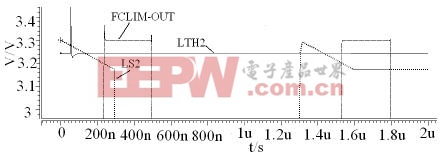

我們采用HSPICE 對圖3 所示的電路進行了比較器功能的模擬,由圖4 可見當電感電流上升時,采樣得到的電壓LS2 下降,當功率管的漏端電壓下降到一定程度,使得LS2 達到PFM 限流比較器門限LTH2 時,比較器輸出高電平至控制邏輯模塊,從而使芯片進入PFM工作模式以延長電池壽命。此外,比較器延遲70nS。

圖4 PFM 限流比較器的仿真

5 結束語

本文成功地設計出一款應用到DC/DC 芯片上的PFM 限流比較器,并通過HSPICE 進行了仿真。結果表明:電路結構簡單,功耗低,響應速度快,完全滿足新一代DC/DC 產品的要求,且預計投入市場之后將獲得上百萬元的效益。

本文作者創新點:本文采用的DC-DC 降壓變換器結構采用同步校正器代替傳統的二極管,極大地提高了DC-DC 降壓變換器的效率,可達到95%左右。基于該DC-DC 降壓變換器結構設計了一個新穎的基于Step-Down PWM 電源管理芯片的PFM 限流比較器電路,在輕載時使芯片進入PFM 工作模式,因此能夠延長電池壽命并且大幅度的提高Step-DownPWM 電源管理芯片的效率。

評論