基于SoPC的FIR濾波器設計與實現

數字濾波(idgital filter)是由數字乘法器、加法器和延時單元組成的一種計算方法。其功能是對輸入離散信號的數字代碼進行運算處理,以達到改變信號頻譜的目的。數字濾波器根據頻域特性可分為低通、高通、帶通和帶阻4個基本類型;根據時域特性可分為無限脈沖響應(infinite impulse response,IIR)濾波器和有限脈沖響應(finite impulse response,FIR)濾波器。FIR濾波器不存在穩定性和是否可實現的問題,容易做到線性相位,故在數據通信、圖像處理等領域廣泛應用。

目前,FIR濾波器的硬件實現有以下幾種方式:一種是使用通用數字濾波器集成電路,這種電路使用簡單,但是由于字長和階數的規格較少,不易完全滿足實際需要;雖然可采用多片擴展來滿足要求,但會增加體積和功耗,因而在實際應用中受到限制。另一種是使用DSP芯片,DSP芯片有專用的數字信號處理函數可調用,實現FIR濾波器相對簡單,但是由于程序順序執行,速度受到限制。而且,就是同一公司不同系統的DSP芯片,其編程指令也會有所不同,開發周期較長。還有一種是使用可編程邏輯器件,如FPGA(field programmable gate array),即現場可編程門陣列,有著規整的內部邏輯塊整列和豐富的連線資源,特別適合用于細粒度和高并行度結構的FIR濾波器實現,相對于串行運算主導的通用DSP芯片來說,并行性和可擴展性都更好。

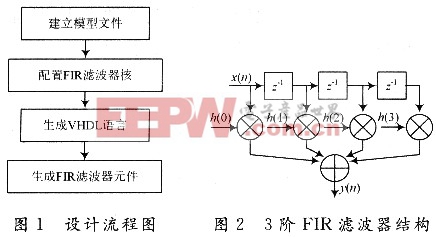

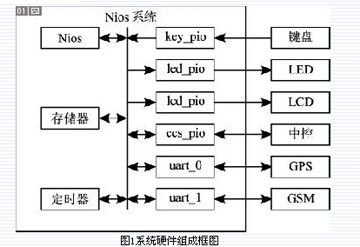

本文介紹一種基于SoPC的FIR濾波器設計方案,設計流程如圖l所示。該設計方法程序簡單,調試方便,得到的FIR濾波器精確度高。

1 FIR濾波器原理

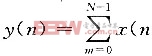

FIR數字濾波器是一種非遞歸系統,其沖激響應總是有限長的,其系統函數可以記為: ,最基本的FIR濾波器可用下式表示

,最基本的FIR濾波器可用下式表示 是輸入采樣序列;h(m)是濾波器系數;N是濾波器的階數;y(n)表示濾波器的輸出序列。也可以用卷積來表示輸出序列y(n)與x(n),h(n)的關系:

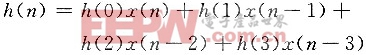

是輸入采樣序列;h(m)是濾波器系數;N是濾波器的階數;y(n)表示濾波器的輸出序列。也可以用卷積來表示輸出序列y(n)與x(n),h(n)的關系:

y(n)=x(n)*h(n)

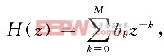

圖2顯示了一個典型的直接T型3階FIR濾波器,其輸出序列y(n)滿足下列等式:

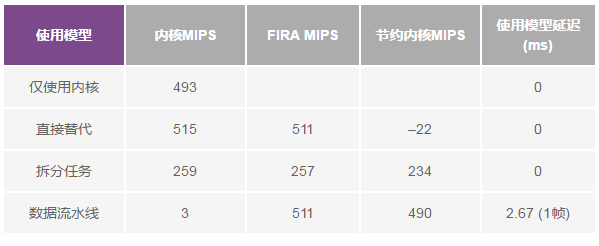

在該FIR濾波器中,總共存在3個延時結,4個乘法單元,1個4輸入的加法器。如果采用普通的數字信號處理器(DSP)來實現,只能用串行的方式順序地執行延時、乘加操作,不可能在1個DSP處理器指令周期內完成,必須用多個指令周期來完成。但如果采用FPGA來實現,就可以采用并行結構,在1個時鐘周期內得到1個FIR濾波器的輸出。不難發現,圖2的電路結構是一種流水線結構,這種結構在硬件系統中有利于并行高速運行。

評論