基于FPGA和DDS技術的正弦信號發生器設計

3 實驗數據測試

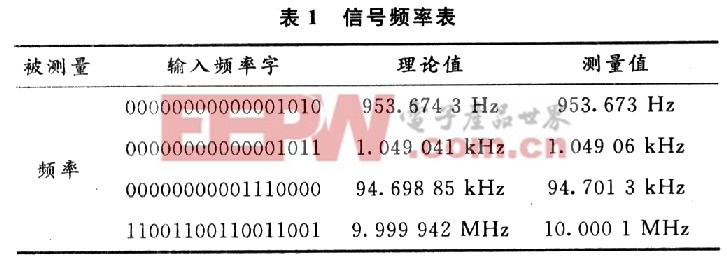

由鍵盤輸入的是二進制頻率控制字,通過數碼管可以顯示出十進制的頻率和相位,將信號發生器的輸出端和雙通道數字示波器接好,任意幾個頻率為1 kHz~10 MHz之間的信號測試結果如表1所示。本文引用地址:http://cqxgywz.com/article/187877.htm

4 結語

本系統設計時,相位字是在編程時就固定的,輸出正弦信號的頻率變化是由頻率字變化引起的,而頻率字的預置是通過鍵盤輸入的,因此能夠得到頻率變化的正弦信號,這樣的信號源能夠很好地滿足需要變頻信號的情況,因此,實用性較強。通過理論計算和實際測量相比較可以看出,基于FPGA的DDS技術實現正弦信號發生器輸出正弦信號頻率范圍較寬、分辨率高、幅度和頻率的精度較高。另外,本系統還很容易擴展,不需要對硬件電路進行較大的修改,只需要修改相應的程序便可實現相應的功能,比如產生PSK,ASK信號等。但是它也有局限性,主要表現在輸出雜散大,這是由于DDS采用全數字結構,不可避免地引入雜散,主要來源有三個:相位累加器相位舍位誤差造成的雜散;幅度量化誤差造成的雜散和DAC非線性造成的雜散。

評論