基于Xilinx FPGA的千兆以太網及E1信號的光纖傳輸

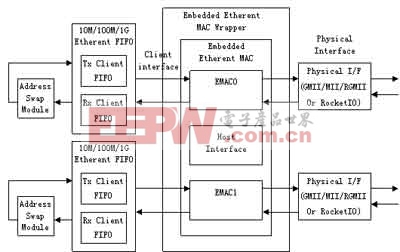

圖4 Virtex-5以太網MAC封裝的模塊結構圖

以太網MAC是一個具有162個端口和79個參數的復雜組件。封裝文件讓你可以僅對特定應用所需端口的參數和接口輕松進行設置。它們的另外一個優勢是簡化了時鐘和物理I/O資源的使用。

以太網MAC封裝。在最低級別,實體化一個單獨的或者雙以太網MAC,同時在CORE Generator GUI中將它的屬性設置成你偏好的選項。所有未使用的輸入端口接地,未使用的輸出端口保持開路狀態。

模塊級別的封裝。在下一層級,對物理接口以及所要求的時鐘資源進行實體化。這包括用于串行接口的RocketIO GTP收發器。同時針對你的配置對時鐘進行優化,并且利用時鐘將輸出同步到你的設計。

LocalLink級別的封裝。在該級別,將FIFO添加到客戶端發送器和接收器接口。FIFO能夠處理接收時壞幀的丟失并且以半雙工模式對幀重新傳輸。LocalLink可以作為后端接口使用。

RocketIO GTP Transceiver

RocketIO是一種高速的串行收發器,采用兩對差分對來進行數據的發送和接收,可以實現兩個單工或一對全雙工的數據傳輸。RocketIO支持622Mb/s~3.75Gb/s的全雙工傳輸速率,還具有8b/10b編解碼(平衡編碼)、時鐘生成及恢復等功能。Aurora協議是為專有上層協議或行業標準的上層協議提供透明接口的第一款串行互連協議,可用于高速線性通路之間的點到點串行數據傳輸,同時其可擴展的帶寬,為系統設計人員提供了所需要的靈活性。

1 PMA和PCS層

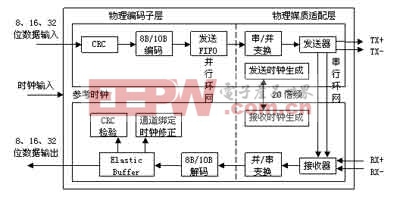

RocketIO包括PMA(物理媒介適配層)和PCS(物理編碼子層)兩個子層,其內部結構如圖5所示。其中PMA子層主要用于串行化和解串,PCS主要包括線路編碼和CRC校驗編碼。

圖5 PMA、PCS內部結構框圖

PMA子層中集成了SERDES,發送和接收緩沖,時鐘發生器及時鐘恢復電路。SERDES是一個串并轉換器,負責FPGA中本地的32位并行數據(也可以是16位或8位)與RocketIO接口的串行數據之間的轉換。采用串行數據收發,可以在高頻條件下很好地避免數據間的串擾。時鐘發生器及時鐘恢復電路用于將時鐘與數據綁定發送,以及將時鐘從接收到的數據流中恢復出來,從而避免了在高速傳輸條件下時鐘與數據分開傳輸所帶來的時鐘抖動等問題。

PCS子層負責8b/10b編碼解碼和CRC校驗,并集成了負責channel綁定和時鐘修正的彈性緩沖。8b/10b編碼可以避免數據流中出現連0連1的情況,便于時鐘的恢復。channel綁定通過在發送數據流中加入P字符來將幾個RocketIO通道綁定成一個一致的并行通道,從而來提高數據的吞吐率。最多支持24個通道的綁定。彈性緩沖可以解決恢復時鐘與本地時鐘的不一致問題,并進行數據率的匹配,從而使得channel綁定成為可能。對Rocket IO模塊的配置,可以通過下面兩種方式進行:靜態特性可以通過HDL代碼設置;動態特性可以通過RocketIO的原語端口進行配置。

評論