32階FIR濾波器的FPGA實現

3 FPGA仿真與驗證

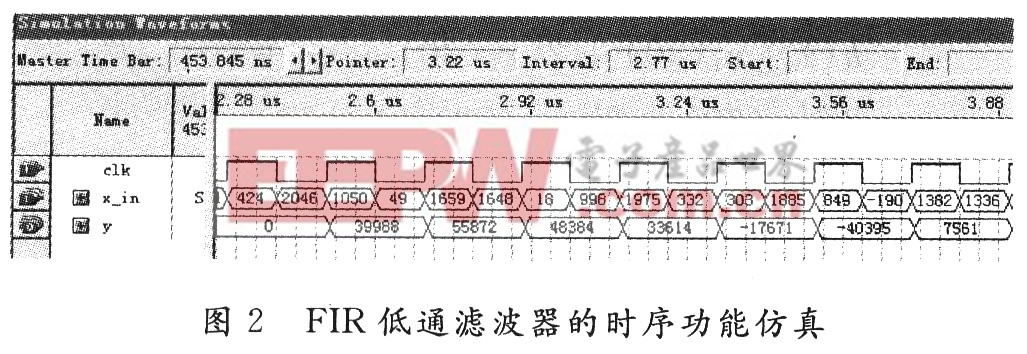

由于直接將大量數據進行硬件仿真驗證很不方便,因此利用Matlab產生一個采樣頻率為100 MHz,頻率分別為1 MHz與30 MHz的兩個正弦信號相加后,作為輸入信號。同樣,浮點變?yōu)槎c,將此信號進行12位量化,并將負數轉化為補碼形式,按照一定格式保存為.vec文件,導入到QuartusⅡ中進行仿真,時序功能仿真結果如圖2所示。本文引用地址:http://cqxgywz.com/article/188447.htm

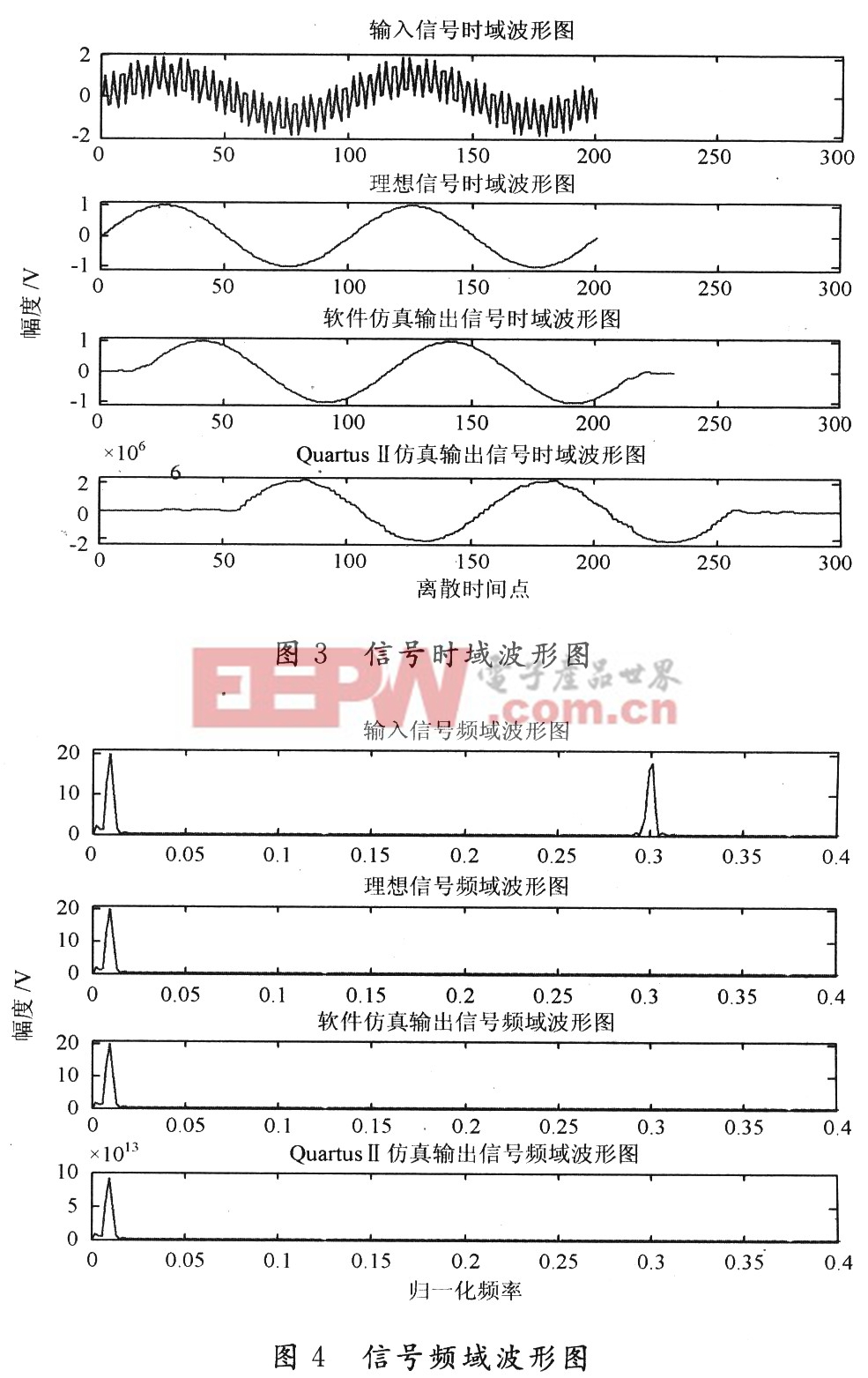

其中,clk為時鐘信號,x_in為濾波器輸入信號,y為濾波器輸出信號。圖2并不能很直觀地看出并行分布式算法產生的濾波效果,可以將QuartusⅡ中.vwf文件轉化為.tbl文件,在Matlab中按照一定形式編程可以得到時域及頻域波形圖,如圖3,圖4所示。

圖3,圖4中,軟件仿真是直接在Matlab中用輸入信號與濾波系數卷積得到的,在時域波形中軟件仿真輸出信號與理想信號相比有一定時間延遲,而QuartusⅡ仿真與軟件仿真結果中幅度的差別是由于硬件輸入量化產生的。

從時域或者頻域波形圖可以看出,頻率為30 MHz的信號被濾除掉,只有頻率為1 MHz的信號通過濾波器,達到了濾波的目的。

4 結 語

本設計選用Stratix系列芯片,最大處理速度可以達到200 MHz以上。本文沒有考慮線性相位的濾波器對稱性,在考慮線性相位的基礎之上結合一些其他算法可以降低器件數量和進一步提高處理速度。由于FPGA器件的可編程特性,在本設計中可以修改濾波器參數,得到高速處理的高通或者帶通數字濾波器,具有一定實用價值。另外,本文利用QuartusⅡ與Matlab聯合仿真,極大地提高了FPGA的設計效率。

評論