閃變信號電路的設計與實現

隨著我國國民經濟的發展,電力網負荷急劇增加,特別是沖擊性、非線性負荷所占比重不斷加大,使電網電壓產生波動和閃變,嚴重影響了電網的電能質量。因此,研究電壓波動與閃變、積極采取措施保證電能質量己成為當前供電部門的一項重要而緊迫的任務。然而如何得到閃變信號成為重要問題,因此,標準閃變信號電路的研究是基于SOPC的電壓波動和閃變檢測與分析的重要內容。

本文提出一種全數字化技術的閃變信號電路,主要研究了該電路的原理、關鍵參數設計準則,并給出了試驗結果。

1 閃變信號電路的構成與原理

1.1 電路構成

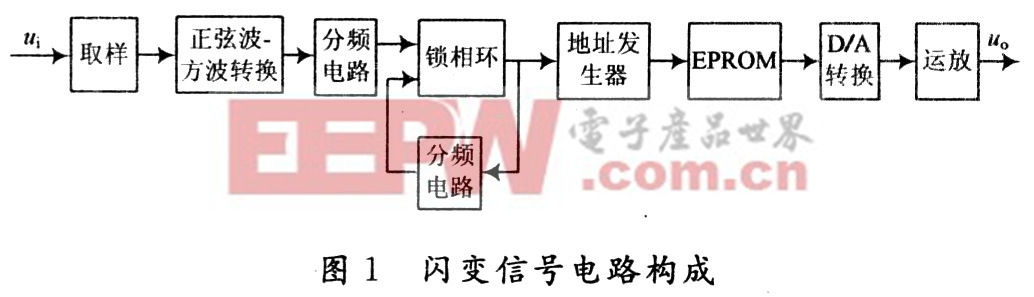

閃變信號電路由電網電壓取樣和正弦波一方波轉換電路、倍頻電路或分頻電路、時鐘信號形成電路(包括鎖相環和分頻電路)、相位同步電路(即地址發生器清零信號形成電路)、閃變信號產生電路(包括EPROM,D/A轉換電路和運算放大器)等五個部分組成,如圖1所示。其基本思想是先將電網電壓ui變換成一個電壓方波信號,將電壓方波信號分頻后(如n=4)得到基準電壓方波信號(頻率即為12.5 Hz),輸入到鎖相環,鎖相環輸出信號經m分頻電路(如m=1 024)后再送回鎖相環,作為基準電壓方波信號的比較信號。當鎖相環處于鎖定狀態時,鎖相環輸出頻率為基準電壓方波信號m倍的時鐘信號。該時鐘信號送人地址發生器,然后依次讀取出事先固化在EPROM中的數字化的標準閃變信號,再經過D/A轉換和運算放大器,變換成閃變信號電壓。

1.2 電路原理

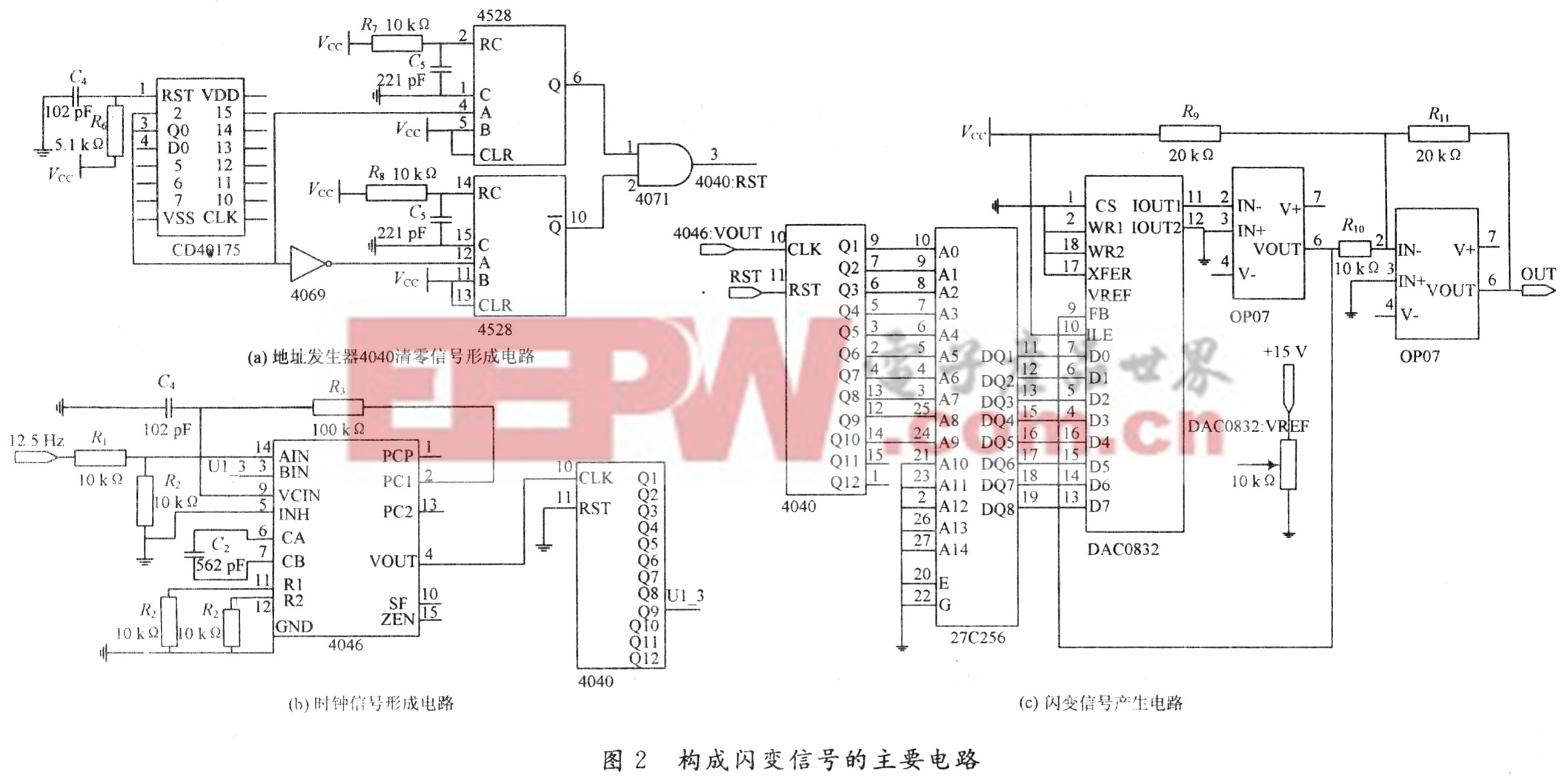

閃變信號電路的主要電路如圖2所示。

電網電壓取樣與正弦波一方波轉換電路由變壓器取樣、過零比較器組成,其輸出的電壓方波信號與電網電壓同步。

相位同步電路即4040清零信號的形成電路,如圖2(a)所示。將基準方波電壓信號送入D觸發器40175分頻,輸出6.25 Hz的方波(保證一周產生一次清零信號),再將其信號及其經過非門4096后的反相信號一起送入單穩態觸發器4528,經或門4071后得到4040的清零信號,以實現4040的1 024分頻計數,從而保證對EPROM中數據的正確讀取。

時鐘信號形成電路如圖2(b)所示。將基準電壓方

波信號輸入鎖相環,由鎖相環輸出電路所需的時鐘信號。在鎖相環的鎖定狀態下,該時鐘信號頻率為基準電壓方波信號頻率的1 024倍。該時鐘信號經分頻器4040實現1 024分頻,所得信號作為鎖相環的比較信號。將此時鐘信號送人地址發生器4040。

閃變信號產生電路由地址發生器4040,EPROM27C256,DAC0832和OP07組成,如圖2(c)所示。其核心是EPROM27C256和DAC0832。可事先由Matlab編程產生的一個周期的閃變信號,再由Matlab進行1 024分頻離散采樣,算好其幅值后按序排成數據表存入EPROM中。

鎖相環輸出的時鐘信號輸入到地址發生器4040,4040順序掃描存入EPROM中的數據表,代表閃變信號幅值的8位二進制數被送到DAC0832,將數字量轉換成模擬量輸出。周而復始,產生一串階梯閃變波形。由于DAC0832為電流型器件,因此必須與運算放大器連接,構成D/A轉換器。

2 關鍵電路參數設計

鎖相環CD4046是整個電路關鍵器件之一,其鎖定范圍和外圍電阻R4,R5及電容C2有很大關系。R3和C1構成了鎖相環CD4046的外接低通濾波器。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論