FPGA實現FIR抽取濾波器的設計

3 濾波器系數的求取

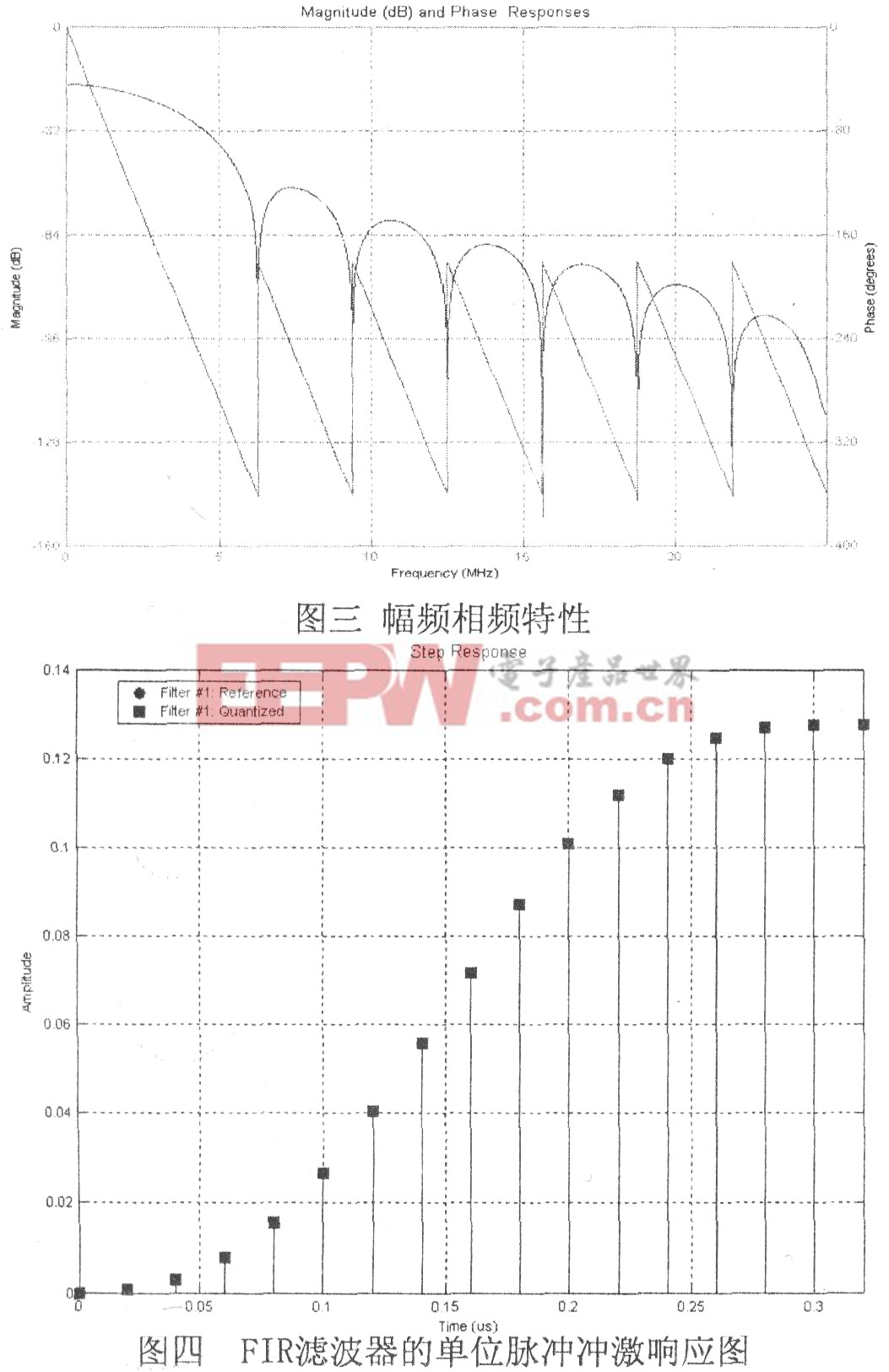

使用Matlab集成的濾波器設計工具FDAtool,可以完成多種濾波器的數值設計、分析與評估,設計16階低通濾波器參數如下:

采樣頻率:Fs為50MHz,濾波器歸一化截止頻率:Fc為0.4MHz,輸入數據位寬:8位,輸出數據寬度:16位FDAtool采用漢寧窗函數(Hanning)設計16階線性相位FIR數字濾波器,并提取其特性參數h(n)浮點數值。本文引用地址:http://cqxgywz.com/article/188940.htm

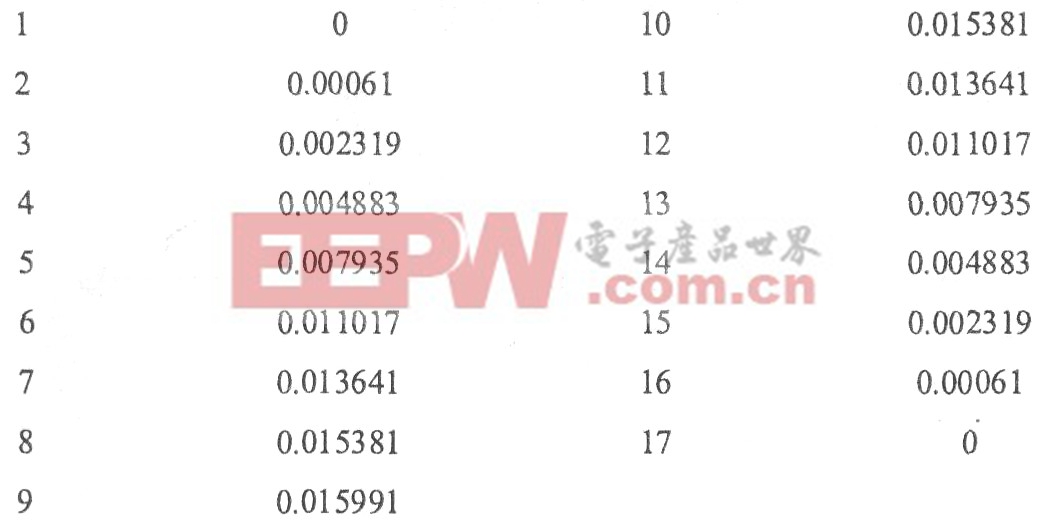

MATLAB中算出的系數h(n)的值是一組浮點數,進行浮點值到定點值的轉換,用16位二進制補碼表示為

濾波器抽頭數是16個,考慮到線性FIR濾波器的偶對稱特性,只考慮8個獨立濾波器抽頭數,則需要一個28×8的表(其中指數8指的是8個濾波器抽頭數,后面的8指的是輸入數據的位寬)。但是Virrex―e FPGA只能提供4輸入的杏找表,所以要對查找表的地址進行電路分割。將8位地址線分為高4位和低4位,分別作為兩個24×8的查找表的地址輸入,從而指數倍地節省了硬件資源。

4 主程序及仿真

在時鐘和計數器的控制下,根據查找表輸出結果位權的不同,將輸入數據向左移動相應的位數,低位按照位權的不同補上個數相當的“0”,然后將移位數據進行累加操作,輸出最終濾波結果,這里的結果依舊是用二進制數據表示的,只是位數因為移位和累加操作增加了8位。

評論