基于VHDL的QPSK調制解調系統設計與仿真

3 QPSK數字解調器仿真

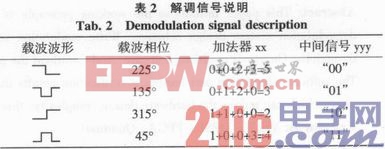

根據解調原理,MPSK解調電路的VHDL模型如圖1所示,輸入時鐘信號clk及使能信號start,當start為高電平時才進行MPSK解調,輸入已調信號x,設輸入相位為225°,315°,45°,225°,135°,315°,45°,315°,225°,225°,225°,315°的載波波形,將一個信號周期分成4份,高電平權值分別為0,0、0、0.低電平權值分別1、1、2、3,如表2所示。本文引用地址:http://cqxgywz.com/article/189500.htm

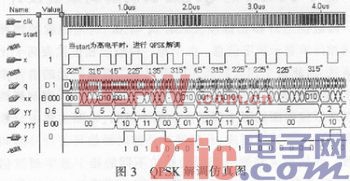

由圖1可知,當調制信號x為低電平時,譯碼器1根據計數器q值。送入加法器XX相應的數據。經過反復的運算后,當q值為0和1時,加法器xx再將運算結果送到寄存器。譯碼器2根據yy數據通過譯碼,輸出2位并行信號YYY。如表2所示,中間信號yy與YYY的關系為:5對應“00”;3對應“01”;2對應“10”,4對應“11”。并行信號YYY進行并/串轉換后得到Y值。最終實現了相位為225°的載波,對應輸出Y值為“00”相位為135°的載波,對應輸出Y值為“01”;相位為315°的載波,對應輸出Y值為“10”;相位為45°的載波,對應輸出Y值為“11”。sta rt信號為高電平時開始解調信號,輸出結果(y)為0010 11 00 01 10 11 10 00 00 00 10,仿真結果如圖3所示。

4 結束語

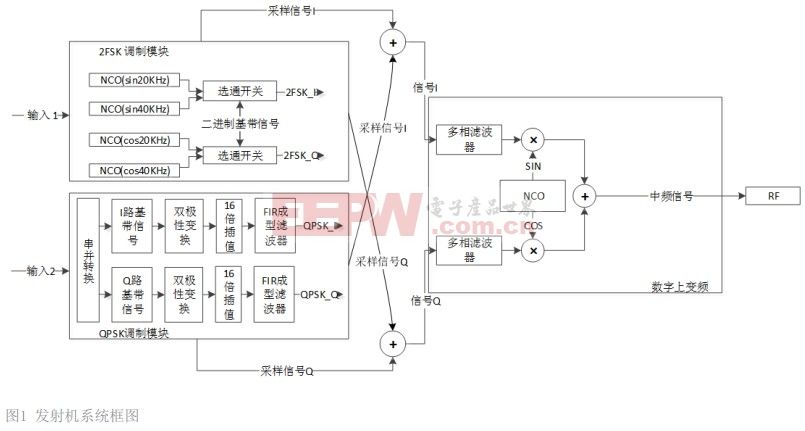

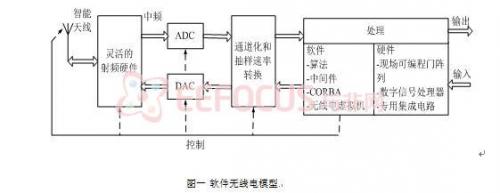

本文基于VHDL方式實現了QPSK數字調制解調電路的設計,通過QuartusII軟件建模對程序進行仿真,并通過引腳鎖定,下載到FPGA芯片EP1K30TC144—3中,軟件仿真和硬件驗證結果表明了該設計的正確性和可行性,對比傳統的電路設計有著明顯的優點,簡化設計,降低硬件電路的復雜性,并由于采用FPGA芯片,提高了設計的靈活性和可移植性,減小硬件設計的復雜性,便于移植維護和升級的特點。如為了防止相位模糊現象,采用差分編碼,采用QDPSK調制解調系統,只需更改軟件程序即可。

評論