基于Altera浮點IP核實現浮點矩陣相乘運算的改進設

3.2 計算結果仿真

對改進的設計進行仿真,采用A9×16數據與B16×8數據相乘,獲得計算結果仿真如圖4所示。

從圖4可見,loadaa、loadbb、calcimatrix三者的時序滿足浮點矩陣運算的時序要求,在前兩者數據加載后,加載calcimatrix上升沿,進行矩陣相乘。在outvalid為高電平時輸出數據,同時完成信號done輸出低電平。在輸出結果上,共分為9個大組,各大組有8個數據,共組成72個數據結果,其中顯示了第一部分輸出結果,獲得與Matlab仿真相近的計算結果,在精度上相差不到萬分之一。

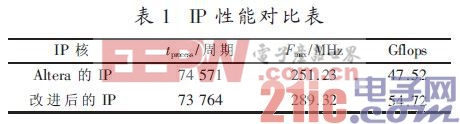

從表1中可以看出,改進后的IP核在處理時間上縮短了807個周期,同時在最高運行時鐘上提升了15%,系統整體的持續性能增加了7.2 Gflops。

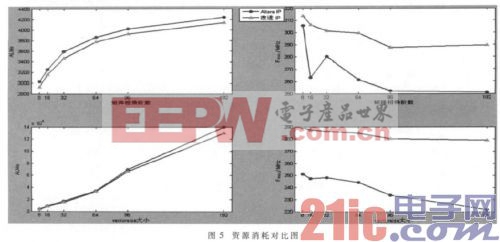

依據改進前后的IP核,使用Quartus9.1軟件進行綜合布局布線,映射到Stratix Ⅲ EP3SE110F780C2器件中,可獲得相應的資源對比圖如圖5所示。由于采用的都是并行浮點乘加運算,所以在乘法器資源的消耗上不變;同時由于只是在存儲器的存儲方式上作出變動,所以二者的存儲資源相等。從而只需要對圖中顯示的矩陣階數、vectorsize大小進行比較即可,而浮點計算性能與最高時鐘頻率變化方向相同,所以只對ALM數量及最高時鐘頻率進行對比。

從圖5中資源消耗對比可見,當設定vectorsize為固定值8(圖5左半部)時,隨著矩陣階數的增加,改進后的IP核在ALM資源消耗上較改進前數量上有一定的減少,在最高時鐘頻率上都有小幅度提升,這是因為矩陣輸入時消耗時間過長;當設定矩陣階數為192×192(圖5右半部)時,隨著vectorsize值的增加,改進后IP核在ALM數量上有所減小,在最高時鐘頻率上則有小幅度提升,且波動幅度在3.4%左右。可見,改進后IP核比原Altera的IP核綜合性能有所提升。

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論