基于消息機制的片上多處理器系統的研究

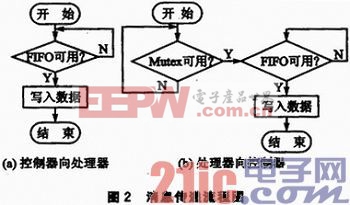

2.2.1 控制器到處理器方向

控制器到處理器方向的連接屬于一對多的模式,每條通路各自獨立,因此該方向上的傳遞比較簡單,由控制器直接向目標FIFO寫入數據即可。該方向的傳遞流程圖如圖2(a)所示。本文引用地址:http://cqxgywz.com/article/189737.htm

2.2.2 處理器到控制器方向

處理器到控制器方向的連接屬于多對一的模式,當處理器同時有消息要傳遞給控制器時會引起沖突。為解決該沖突,系統引入了互斥核。因此該方向上的消息傳遞時需要先鎖定互斥核,才能向控制器的FIFO寫入消息數據。該方向的傳遞流程圖如圖2(b)所示。

2.3 消息的讀取

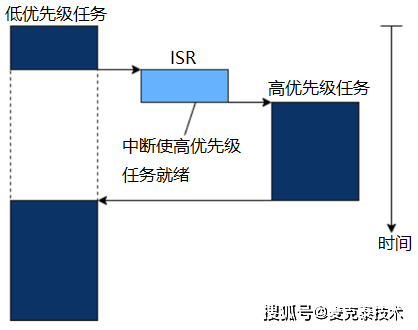

消息的讀取過程為處理器從消息存儲器FIFO讀出數據的過程。由于采用的是雙端口FIFO,數據的寫入與讀取可同時進行。但由于處理器可能存在中斷、寫入與讀出速率不一致等原因,因此消息的讀取采用異步讀取的方式,即判斷FIFO中的數據個數,先讀取消息的前兩個字節,獲得該消息的長度,然后根據該長度等待消息傳遞完畢,再一次性讀取剩余消息數據。

2.4 消息的處理

消息讀取完之后,首先發送確認消息給發送者,表示成功收到了消息。然后根據洧息中的類型跳轉到該類型的處理函數,接著再根據消息中的子類型跳轉到該子類型的處理函數。最后,當任務執行完之后發送任務結束消息。

2.5 數據移動

當系統中有大量的數據需要移動時,為了減少系統的開銷,加入DMA核。數據的移動由DMA核控制,而DMA核由控制器進行控制。因此,從處理器如果有移動數據的需要,需要用消息先通知控制器,然后由控制器控制DMA進行移動。圖3為控制器利用DMA進行數據移動的流程圖。

2.6 容錯性設計

當系統長時間運行時,不排除處理器出現問題的可能性,因此需要引入容錯性設計,保證系統能正確運行。

首先,主控制器中定義一個從處理器列表。從處理器初始化完成時,發送初始化完成消息,主控制器對發送消息的從處理器進行登記,并添加到列表。

接著,主控制器中定義一個任務結構,包含任務所屬的組、任務ID、任務允許最長處理時間、任務開始處理的時間等字段。運行時,主控制器根據事先設計的程序生成任務列表,然后根據從處理器列表分配任務,并記錄任務處理開始時間。

然后,主控制器反復查詢任務列表,檢查任務時間。當發現任務超時,則重新分配該任務,使得系統仍能正常工作,并將處理該任務的從處理器從列表中別除,發出警報。

3 實驗與結果

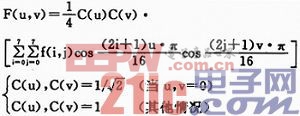

為了驗證該系統的可行性及性能,本文采用JPEG編碼器(以DCT變換為基礎的有損壓縮算法)作為該系統的測試程序。DCT算法的大致流程為:對于一塊最小數據處理單元(MCU),先把數據從空間域變換到頻率域,從而去除數據的冗余度;量化器用加權函數來產生對人眼優化的量化DCT系數,同時熵編碼器將量化DCT系數的熵最小化。

其中前向DCT的變換公式如下:

評論