CPLD的串口電路設計

2. 發送模塊

發送部分采用狀態機t_state 進行編程,共設兩個值:t-start 和t_shift,分別表示發送開始以及發送保持狀態。復位鍵按下時設置到t-start 狀態,并將發送數據位設為“1”, 發送的數據位數計數為0,在t-start 狀態,狀態機將處于這一個狀態并等待波特率計數信號的電平上升沿到來。上升沿到來時,依據t_state 狀態的不同值做不同處理,如果是t-start 開始狀態則先讀待發送的數據,并發送開始位“0”,然后將狀態轉到發送保持t_shift 狀態,在發送保持t_shift 狀態,不斷判斷發送的數據位數是否滿8 位,如果滿了則回歸t-start 狀態,否則繼續發送,保持在t_shift 狀態,為避免干擾將其余情況下的狀態自動跳轉到t-start 狀態。程序如下:

PROCESS(baud_rate,reset,data)

-- 數據發送部分

VARIABLE t_no:INTEGER RANGE 0 TO 8;

-- 發送的數據各位的位序號

VARIABLE txds:STD_LOGIC;

VARIABLE dtmp:STD_LOGIC_VECTOR(7

DOWNTO 0);

BEGIN

IF reset='0' THEN

t_state=t_start;

txds:='1';

t_no:=0;

ELSIF baud_rate'event AND baud_rate='1' THEN

CASE t_state IS

WHEN t_start=>

dtmp:=data;

txds:='0'; -- 發送開始

t_state=t_shift;

WHEN t_shift=> IF t_no=d_len THEN

txds:='1'; -- 發送結束

t_no:=0;

t_state=t_start;

ELSE

txds:=dtmp(t_no); -- 發送一字節數據

t_no:=t_no+1;

END IF;

WHEN thers=>t_state=t_start;

END CASE;

END IF;

txd=txds;

END PROCESS;

3. 數據接收模塊

接收部分采用狀態機進行編程,共設兩個狀態:

r-start 和r_shift 分別表示接收開始以及接收保持狀態;復位鍵按下時設置到r-start 狀態,并將待接收存放數據的data 賦值為“00000000”, 在r-start狀態,接收狀態機將處于這一個狀態并等待波特率計數信號的電平上升沿到來。波特率發生模塊的計數上升沿到來,依據狀態的不同值做不同處理,如果是r-start 接收開始狀態則等待開始位信號,檢測到rxds=‘0’的開始位信號好轉到r_shift 接收保持狀態,r_shift 接收保持狀態會不斷判斷接收的數據位數是否滿8 位,如果滿了則回歸r-start 狀態,否則繼續接收,保持在r_shift 接收保持狀態,為避免干擾將其余情況下的狀態自動跳轉到r-start 接收開始狀態,程序與發送部分類似,此處省略。

三、串口通信的VHDL程序仿真結果

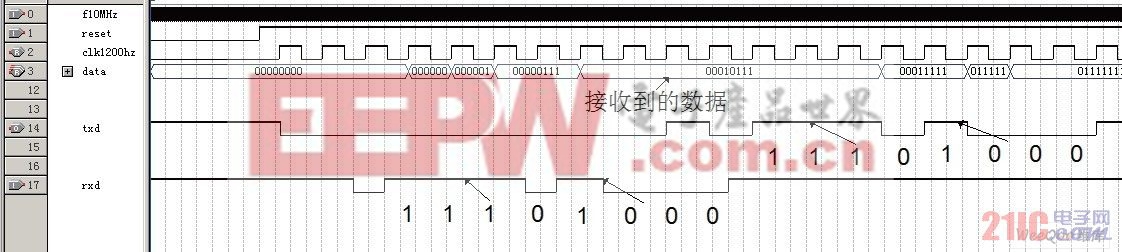

串行口通信的仿真結果如圖2 所示。從圖中可以看出,每發送完一個字節,即8 位數據后,線路上將輸出一個高電平,之后又開始傳送下一個字節。

同樣,仿真波形顯示,有效數據到達接收管腳rxd之前,線路上保持為高電平,直到收到一個低電平起始位,將該起始位后的8 位數據串行接收后依次送到保存接收結果的信號data 的各位。

圖2 串行口通信仿真波形圖

串口通信的硬件驗證

將程序通過在系統編程下載入配套的CPLD 電路板進行硬件驗證,按照以下步驟進行。

(1)確定管腳對應關系:

串行接收管腳rxd 與max232 的12 腳R1OUT對應; 串行發送管腳txd 與max232 的11 腳T1IN對應;復位信號reset 與按鍵S1 對應。

(2)由QUARTUS II 進行管腳分配:

f10MHz 在MAXII 芯片上對應的管腳號為12 ;S1 在MAXII 芯片上對應的管腳號為21 ; rxd 在MAXII 芯片上對應的管腳號為89; txd 在MAXII 芯片上對應的管腳號為90。

(3)電平定義:

按鍵S1 按下時表示輸入信號為低電平。

應用“ 串口調試助手” 進行驗證, 在發送窗口隨機輸入需要發送的字符,可以發現由PC 機發給CPLD 的字符被CPLD 傳送回來并在接收窗口顯示出來。在批量隨機數據發送后分析:在傳輸時19.2kb/s 傳輸速率下,誤碼率達10-8。

分頻器相關文章:分頻器原理

評論