端接電路的串擾詳細介紹

本文引用地址:http://cqxgywz.com/article/190126.htm

如果電阻的布局是交錯的,如圖6.18所示,就要用交疊長度來代替上式中的Y。

2、相鄰表面貼裝電阻的串擾

表面貼裝電阻本身距離電路板比較近,與實芯電阻相比,可以大大降低串擾系數。為了取得最好的效果,使地平面層接近電路板外層表面,直接把地層埋在表面貼裝元件下面,這樣可以減小上式中的參數H、降低串擾。

3、單列直插(SIP)端接電阻的串據

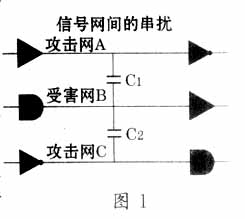

這些器件的效果可能好,也可能不好,這要取決于其內部的走線。圖6.19顯示出了單接地引腳端接電阻的共同電流路徑,這個共同電流路徑會在該封裝的電阻間引入大量的耦合電感。

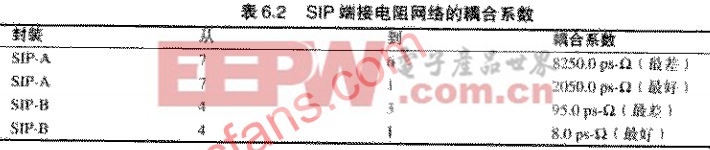

表6.2列出了0.1IN間距SIP封裝電阻排的典型耦合系數。封裝SIP-A包含7個電阻,采用8引腳的封裝,一端有公共的地線引腳。在封裝SIP-A中,電阻7距離地線引腳最遠,封裝SIP-B包含4個電阻,采用8引腳的封裝,每個電阻都有獨立的地,所有的電阻都是50歐,獨立SIP-B封裝比公共地網絡的性能幾乎好100倍。

采用式 可以把這些耦合系數轉換成耦合噪聲電平。

可以把這些耦合系數轉換成耦合噪聲電平。

評論