LVDS信號的PCB設計和仿真分析

1.3.2 串擾

LVDS差分對之間的間距為小于等于線寬,差分對之間的間距為>3倍的線寬,這樣可以減少不同LVDS對之間的信號耦合,避免引入共模噪聲,同時在各個LVDS差分對的空間可以通過鋪地,并打過孔到“GND”層,讓不同1 vds對之間的等效耦合電容為無窮小,以減少相互之間的串擾。

1.3.3 地彈

所謂“地彈”,是指芯片內部“地”電平相對于電路板“地”電平的變化現象。以電路板“地”為參考,就像是芯片內部的“地”電平不斷的跳動,因此形象的稱之為地彈(Ground Bounce),在設計中,對于信號的回流路徑進行處理,讓信號路徑和回流路徑盡量靠近,增大之間的互感,同時對于回流路徑要避免分割現象的發(fā)生,去耦電容要盡量靠近信號的地引腳。

1.3.4 長度匹配

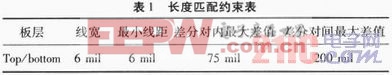

LVDS信號頻率可達到600 MHz以上,所以差分線要求嚴格等長,差分對內最好不超過10 mil,如果頻率低于600 MHz,這個約束值可以適當放寬,但最大應不超過75 mil。不同LVDS對間的布線最大差值不超過200 mil。在Cadence16.3的約束設置中,設置如表1所示。本文引用地址:http://cqxgywz.com/article/190197.htm

1.4 總結

在高速信號下載器中,LVTTL轉LVDS信號的轉換采用TI的sn55lvds31(發(fā)送)和ss55lvds32(接收)芯片進行,最高可以達到800 Mbit/s的傳輸速率。

根據設計要求,對于LVDS信號的布線,總結出以下基本原則:

(1)LVDS信號與TTL信號應相互隔離,最好設置在不同層面上,之間由電源層或地層隔離。

(2)LVDS信號盡量不要有過孔,跨平面分割會造成阻抗不連續(xù)。

(3)差分對內要保持間距一致、平行走線,線間距應小于等于線寬。

(4)差分對間的對內間距保持在10倍以上,差分對間應放置隔離用的接地過孔,每10~25 mil放置一個。

(5)SN55LVDS31/32要盡可能靠近接插件,連線距離越短越好。

(6)差分對應等長走線,以防止信號問相位差導致的電磁輻射。

(7)使用精度為1%的100 Ω表貼電阻,靠近SN55LVDS32輸入端放置(距離不能超過500 mil,應控制在300 mil以內),以匹配傳輸線的差分阻抗。

應避免90°走線,可使用圓弧或45°折線。

(8)LVDS和TTL電平的電源層、地層應分開。

2 LVDS信號仿真分析

仿真主要經過的步驟為,在Tools—Setup Advisor中設計電源網絡和標號,并進行ibis模型的分配,在Cadence中Ibis模型通過Ibs2dml工具轉化為可用的數據格式,對于電容、電阻等無源器件,可以自己建立Espice模型,下面通過約束管理器進行拓撲的提取,對于要提取的網絡使用SigXplorer工具進行,之后即可進行各種仿真。提取的網絡拓撲結構如圖3所示。

評論