基于CPLD的簡易數字頻率計的設計

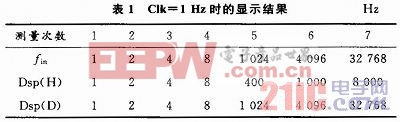

在GW48系列SoPC/EDA實驗箱上下載、調試后,被測信號為fin為十進制,實驗箱上的顯示值為Dsp(H)。Dsp(H)為十六進制,Dsp(D)為十進制,Clk=1 Hz,通過從實驗箱上給出的頻率值來驗證,從表1可以看到顯示結果。

從表1可以看出所顯示的結果與被測信號的頻率一致。從信號發生器中輸入測頻范圍內的任意頻率也可驗證。

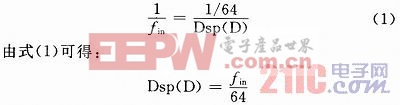

還可以改變控制信號即Clk的大小從而改變測量范圍,當Clk=64 Hz時,理論值為:

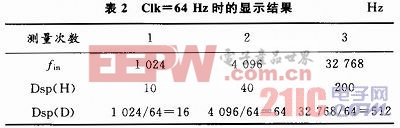

把實驗箱上給出的頻率值做被測頻率,從表2可以看到顯示結果。

從表2可以看出所顯示的結果轉換后與被測信號的頻率一致。

4 結語

采用此種方法設計的簡易數字頻率計簡單、直觀,測頻范圍隨時可根據用戶需要進行調整,占用的CPLD芯片資源較少,不失為一個很好的數字頻率計設計解決方案。由此可見,采用這種技術設計的數字電子系統,大大減少了電路板的尺寸,同時增加了系統可靠性和設計靈活性。

評論