門電路延遲時間的Multisim仿真測試方案

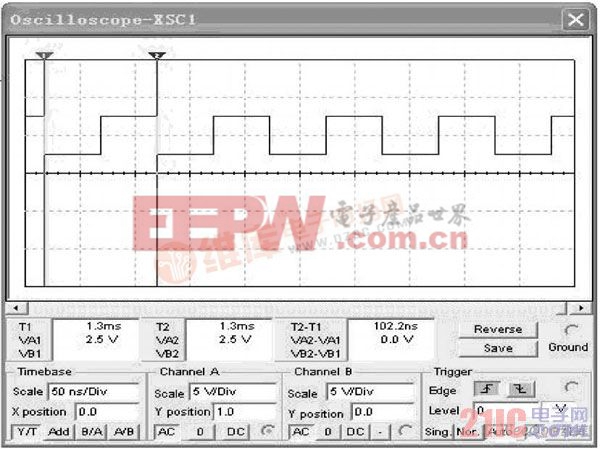

仿真時示波器顯示的波形及振蕩周期測試如圖2所示。

測試的振蕩周期T = 102. 2 ns,則傳輸延遲時間tpd= T/ ( 2N ) = 102. 2/ 10= 10. 22 ns,結果與設定值基本一致。

圖2 圖1 電路輸出波形及振蕩周期測試

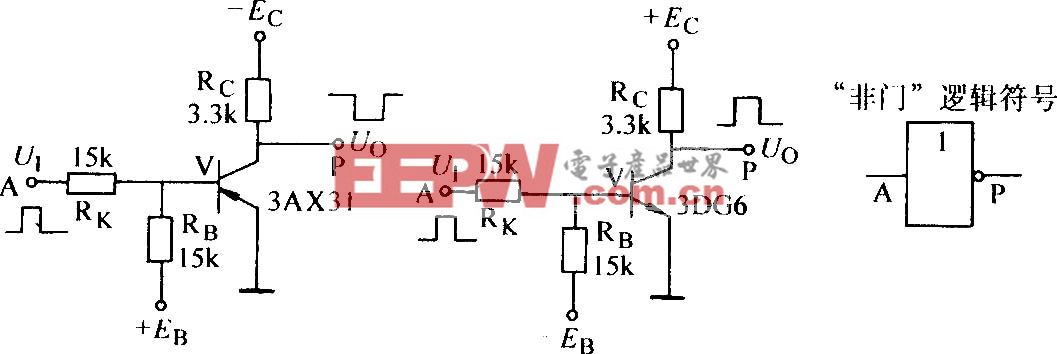

1. 2 測試方案2

將奇數個門首尾相接構成環形振蕩電路,用虛擬示波器測試其中一個門的輸入信號、輸出信號波形及延遲時間。

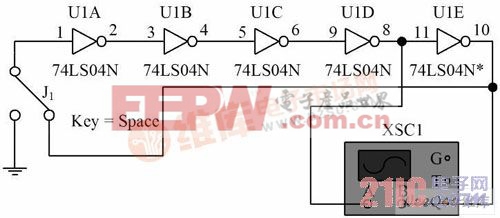

以反相器74LS04N 作為仿真實驗器件,構建仿真實驗電路如圖3 所示。

圖3 測試方案2 的仿真實驗電路

仿真前,可對74LS04N 的上升延遲時間及下降延遲時間進行設置,如設置r ise delay= 10 ns,fall delay=10 ns。

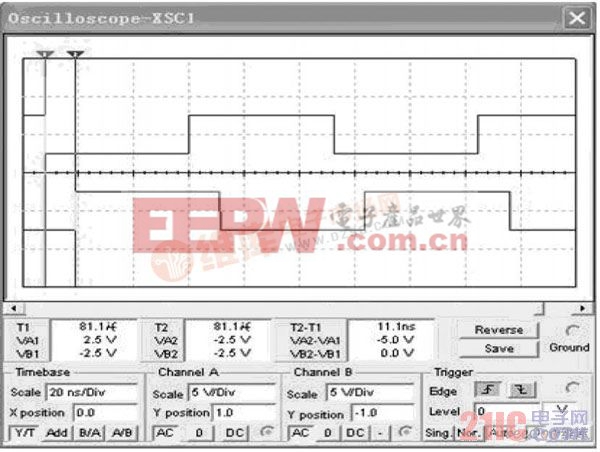

仿真時示波器顯示的輸入信號、輸出信號波形及延遲時間測試如圖4 所示。

圖4 圖3 電路輸入、輸出波形及延遲時間測試

測試的傳輸延遲時間tpd = 11. 1 ns,測量結果與設定值基本一致。

脈沖點火器相關文章:脈沖點火器原理

評論