基于AVR和CPLD的高速數據采集系統

2.1 控制A/D轉換程序設計

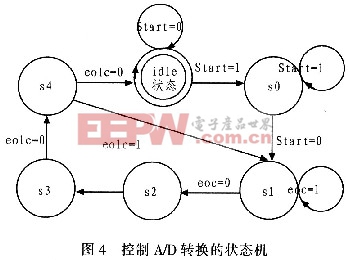

根據控制存儲的要求,首先要設計控制A/D轉換的狀態機,用來確定A/D轉換的狀態,根據MAXl308工作時序特點而設計的控制A/D轉換的狀態機轉換圖如圖4所示。實現控制A/D轉換的狀態機部分主要VHDL程序源代碼如下:

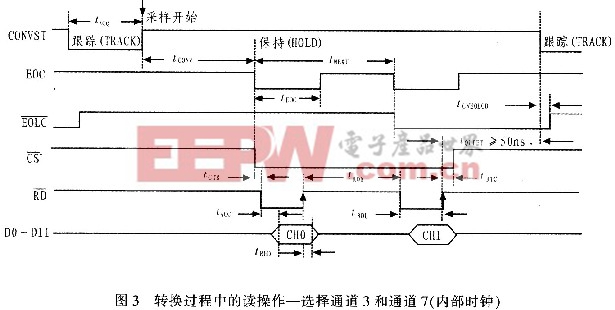

將程序下載至CPLD中運行調試,經過對電路的調試和測量,控制8通道A/D同時轉換的狀態機產生的示波器時序波形如圖5所示,其中,0、1、2、3、4分別對應的是圖3中的CONVST、EOC、EOLC、CS、RD,而第5通道是對FIF0的寫信號。從示波器顯示的波形圖可以看出產生的8個連續的脈沖對應位置完全滿足圖3所要求的時序要求,也就是說在控制器同時控制8路信號的采集時不會出現時序混亂的情況。由此可知,采用本系統中設計的采集程序可以實現同時采集的要求,并且根據采集的脈沖寬度分析可知該系統能滿足采集速度為10 Mb/s的設計要求。

評論