基于CPLD和ISA總線的數據采集系統設計

2.2 數據采集測試程序設計

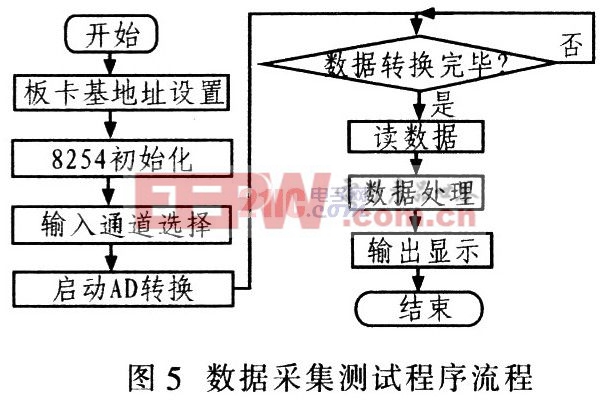

上位機的數據采集測試程序采用C語言設計。因為系統采用ISA接口,所以功能測試無需編寫復雜的應用程序,只需在Win98操作系統里編寫C語言的測試程序即可實現系統的數據采集功能。上位機的數據采集測試程序主要完成:采集系統的硬件初始化、通道選擇、數據采集、數據處理和數據輸出。其程序設計流程如圖5所示。本文引用地址:http://cqxgywz.com/article/191750.htm

3 仿真和實驗結果

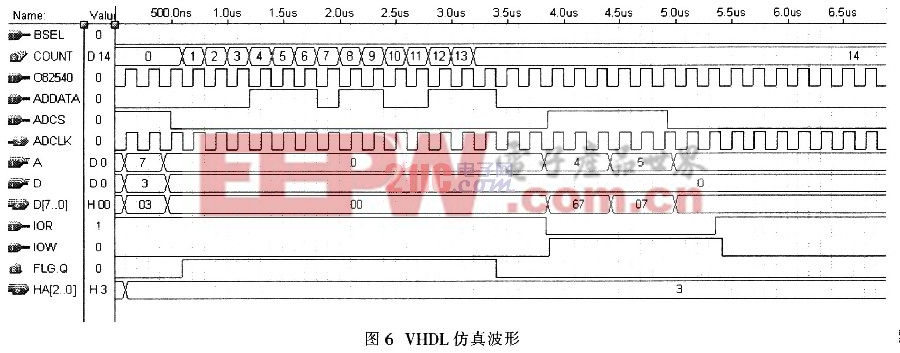

圖6所示為寫入XC9572的VHDL程序的仿真波形,主要是CPLD控制A/D轉換的功能仿真。從仿真波形圖中可以看出,當地址A為7時,寫入通道號3,得到的輸入通道選通信號為3,實現通過上位機選擇輸入通道功能。當ADCS的下降沿到來后開始啟動A/D轉換;ADCS下降沿起的第3個時鐘對應的ADDATA為系統轉換的第1個數據,直到這次轉換完畢。由給定的ADDATA數據得知,串行輸入的數據是767H(011l O110 0111B)。仿真結果中,地址為4時,數據的低8位結果為67H;地址為5時,數據的高8位結果為07H,仿真結果完全正確。

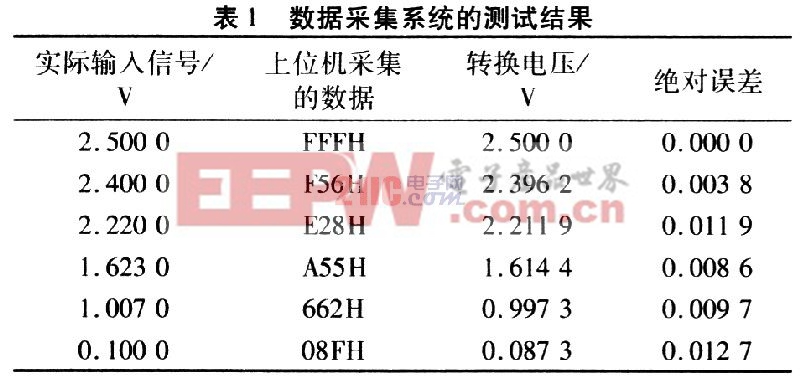

在Windows98下,使用基于C語言的數據采集測試程序,可得到如表l所示的測試數據。從所列數據看出,該數據采集系統采集數據正確,且精度高。

4 結論

基于CPLD的數據采集系統具有硬件線路簡單、精度高、采集速度快的特點。ISA總線和CPLD結合的數據采集系統有其獨特的優勢。該數據采集系統可循環采樣多路(8路)模擬信號采樣。實際測試結果表明該設計方案可行,且具有很高的實用價值。

評論