基于可編程器件的任意進制計數器的設計方法

3.3 仿真測試

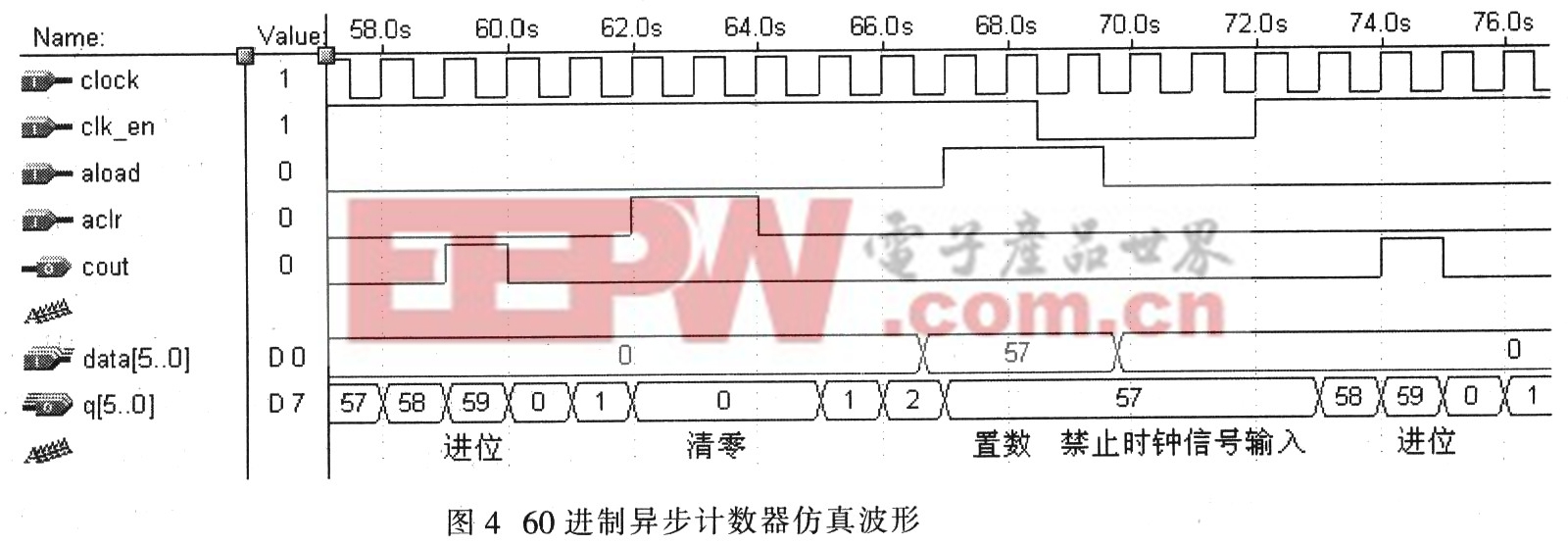

對上述電路進行波形仿真,得到圖4所示的仿真結果。從仿真結果可看出,該計數器實現60進制加計數、清零和置數功能,進位脈沖正常。并將其下載到FPGA器件進行測試,各控制端功能正常,計數器運行良好,性能穩定,達到設計目標。

3.4 方案實現

采用上述方法分別設計出秒、分、時、日計數器及秒脈沖形成分頻器。該分頻器對系統時鐘11.059 2 MHz脈沖進行分頻,從而形成秒脈沖。通過對這些計數器進行組合,共同構成完整的實時鐘模塊。該模塊清零、校時等功能由上位機通過RS485總線對其控制實現。通過裝機運行,測得月誤差在27 s內,達到較高的計時精度。

4 結束語

由于MAX+plus II設計軟件的mega_lpm元件庫(可調參數元件)所提供的庫元件都經Ahera公司的測試和優化.可保證元件的邏輯穩定性,保證可編程器件的芯片利用率及效率達到最優。因此使用LPM庫元件設計計數器電路時,可使設計人員擺脫硬件電路的束縛以及避免軟件編程、調試等煩瑣細節問題,從而系統設計大大提高設計效率。

評論