分布式運算單元的原理及其實現方法

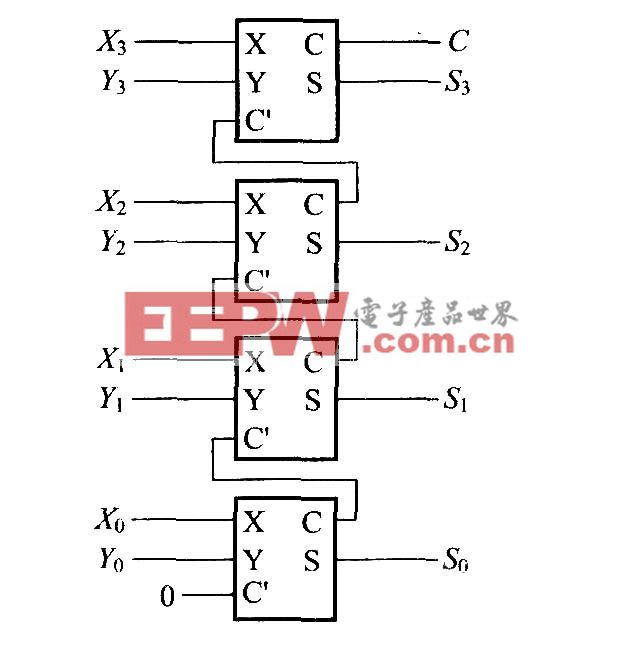

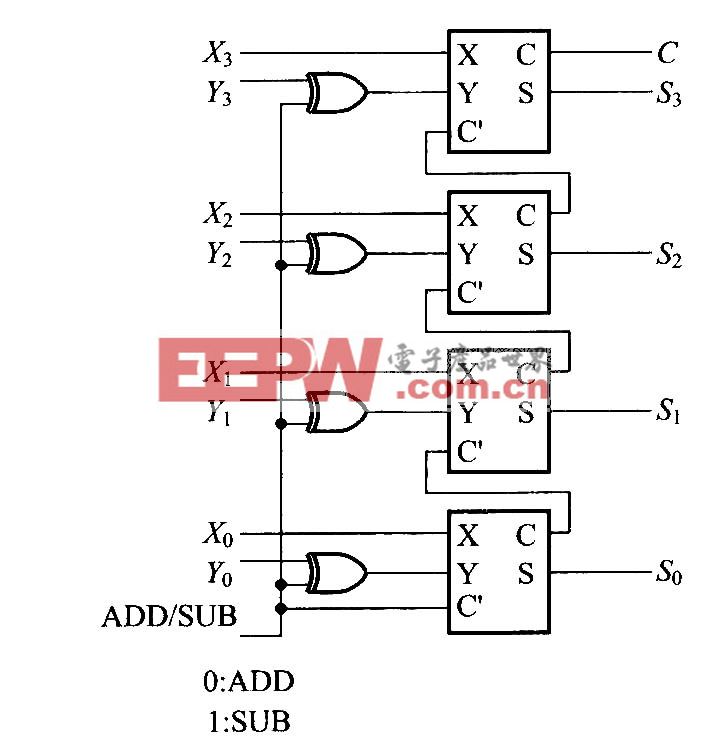

將圖4(a)與圖3進行比較后就可以發現,圖3中的DA查找表由16個輸入變量的同一位進行尋址,而圖4(a)中的DA查找表的尋址是由16個輸入變量的連續兩位進行的,即尋址的位數由16位變成了32位。這樣,查找表的內容也需要相應的改變;而且完成一次運算也由原來的B個時鐘周期變成了需要B/2+1個時鐘周期。

下面介紹一種更易于理解的串并行混合設計方法。

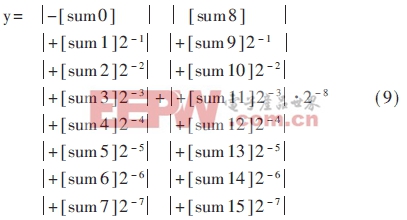

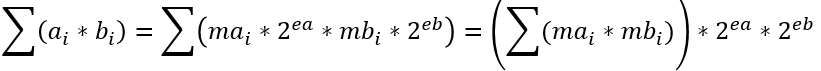

將式(5)改寫成如下形式:本文引用地址:http://cqxgywz.com/article/191941.htm

從式(9)得到流程圖如圖4(b)所示。

實現過程中應該注意DA查找表的內容,累加之前要乘2-1,注意進位等。

從以上給出的兩種串并行結合的設計方法可以看到,只要將式(5)進行適當的變換,還有其它的硬件實現方法,這里就不一一敘述了。

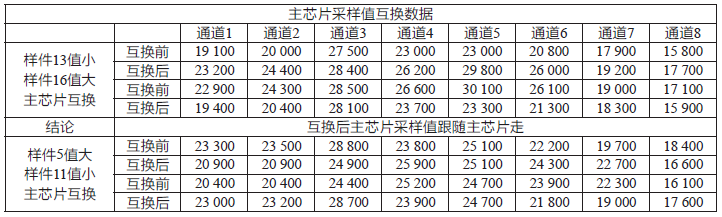

下面給出在K=8、B=16的情況下,不同的DA查找表所占用的資源。Xilinx公司的XC4000系列FPGA的一個CLB可以實現32×1大小的RAM,在圖4(a)中所描述的DA查找表占用2,048個CLB,而在圖4(b)中所描述的兩個DA查找表只占用256個CLB。用一片XC4025即可完成后者,其數據率可達到16MHz。

綜上所述,由于分布式運算單元的應用,改變了傳統的設計觀念,為基于FPGA的DSP設計提出了新的思路,必將在高速的FIR濾波器設計、高速FFT設計中得到廣泛的應用。隨著FPGA集成規模的不斷提高(Xilinx公司Virtex系列已經達到了百萬門級),許多復雜的數學運算已經可以由FPGA來實現,單片FPGA實現系統的設想即將變為現實。

評論