基于Q-Coder算術編碼器的IP核設計與研究

3.2 模塊設計

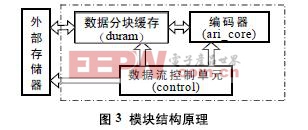

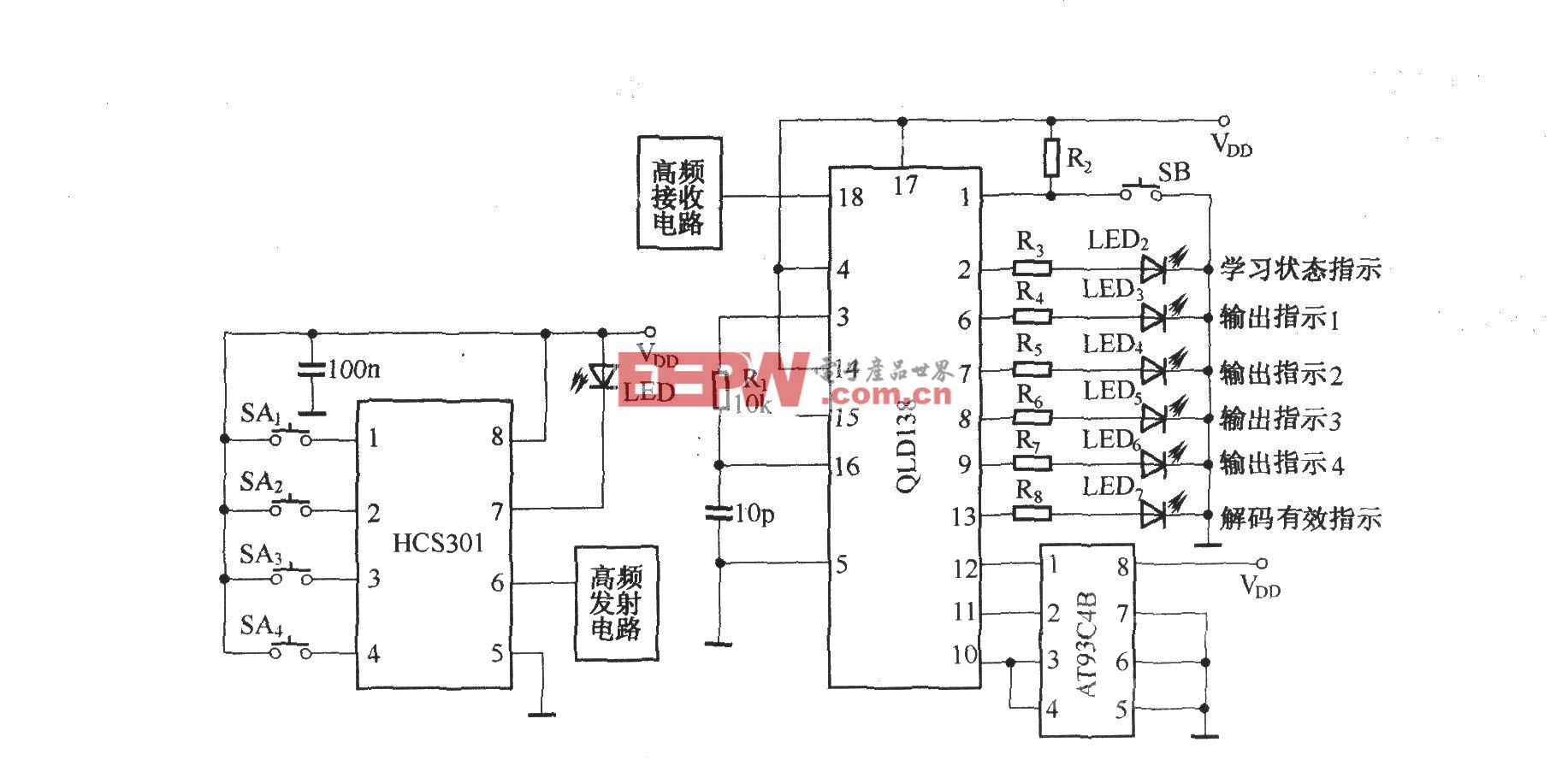

duram是雙口sram作為片內存儲單元存儲輸入的數據,當采用FPGA進行驗證時,直接調用Altera公司的宏功能塊即可;ari_core是實現算術編碼的運算處理單元,包含一個存儲概率估值和當前MPS符號的表以及LPS和MPS編碼子程序;模塊control是數據流控制單元,用于組織片內存儲單元duram和運算處理單元ari_core以及片外sram的數據交換。模塊control是整個設計的控制單元,負責調度以上各個模塊,產生控制和聯絡信號以及地址信號。模塊結構原理如圖3所示。

3.3 電路驗證

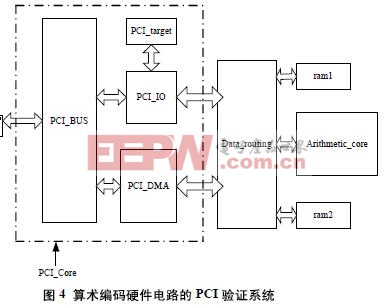

將布局布線后生成的文件下載到自行設計的一塊FPGA的PCI開發板里進行驗證,如圖4所示。板上是一片Altera cyclone系列FPGA ep1c12qfp240,該FPGA含有約25萬邏輯門、30KB內部RAM。PCI接口控制邏輯也是在FPGA中實現[6~8],然后編寫PCI驅動程序和應用程序,先由Jasper軟件處理,抽取軟件中量化模塊處理后的數據,輸入FPGA中進行處理,再將數據返回給軟件中的下一模塊,驗證本文設計的算術編碼IP核的正確性,并計算處理時間。

4 實驗結果與分析

(1)將Verilog源程序在QuartusⅡ軟件中綜合后,得到的參數如下:

1)器件名稱:EP20K200efc484-2x;

2)FPGA時鐘最高頻率:45.18MHz;

3)Total logic elements:3660/8320 (44%)。

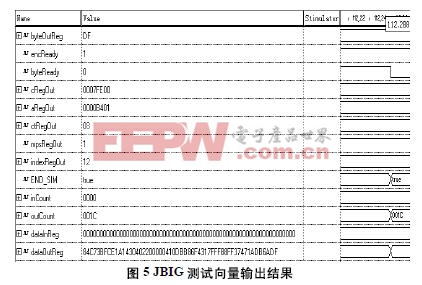

(2)功能驗證。目前,只有JBIG[8]標準中有驗證算術編碼器編碼正確性的測試向量,因此該測試向量被用以測試本文設計IP核的正確性。需要說明的是:JBIG標準中的算術編碼器會產生“FF AC”標志位[8],而JPEG2000中的MQ-Coder算術編碼器并不產生該標志位[1]。

將JBIG中的測試向量作為輸入,經過本文設計的算術編碼IP核處理后的結果如圖5所示,由圖5可知本文設計的算術編碼IP核完全正確。

(3)由概述可知,Jasper軟件具有一定的權威性,因此在實驗中被使用。表1列出了對于同一個圖像文件,Jasper軟件中算術編碼模塊執行所需的時間和本文設計的算術編碼IP核執行所需的時間以及兩者時間之比。

5 結論

本文提出的一種實現算術編碼的集成電路IP核,經過仿真和FPGA驗證,能夠符合JPEG2000標準,仿真結果表明,在相同的條件下,該IP核編碼所需時間僅約為軟件編碼所需時間的40%,從而大大提高了算術編碼的效率,使得將來其應用于實時處理系統成為可能;并且將來可以定制所需的ASIC電路,用于新一代數字照相機等具有廣泛市場前景的項目。

評論