基于DDS驅動PLL結構的寬帶頻率合成器設計

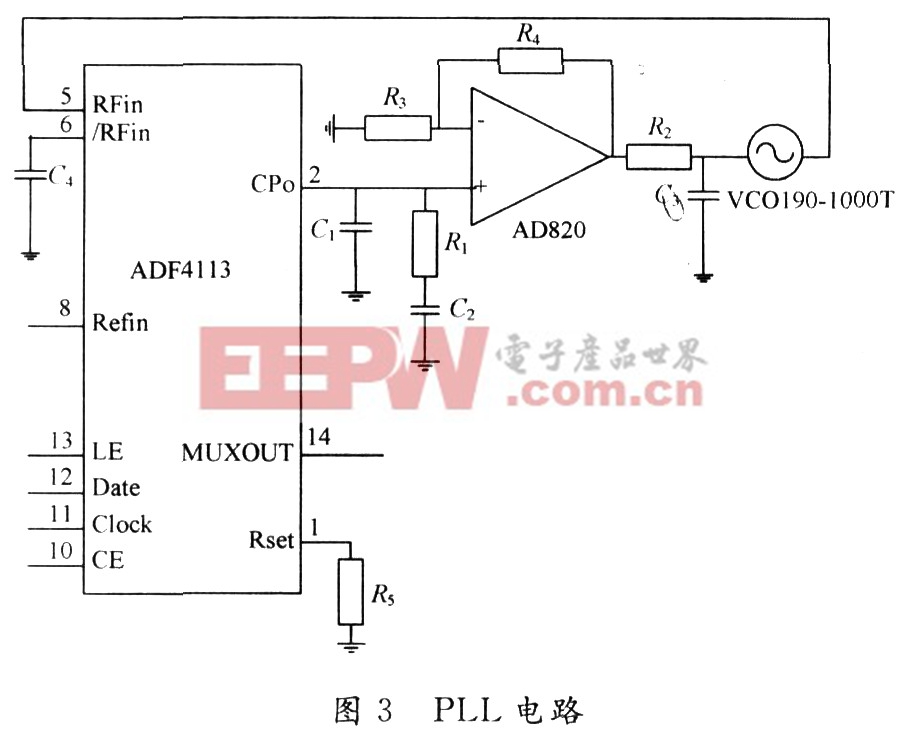

PLL模塊在該設計結構中尤為重要。在此采用ADF4113鎖相環芯片。ADI公司研制的數字鎖相頻率合成器ADF4113,最高工作頻率可達4 GHz,主要應用于無線射頻領域,用以構成數字鎖相環,鎖定某一頻率。該電路內部資源主要包括可編程的模分頻器:8/9,16/17,3z/33,64/65;可編程的14位參考頻率分頻器;可編程的射頻信號分頻器;3線串行總線接口;模擬和數字的鎖定狀態檢測功能。該芯片的最高鑒相頻率達到55 MHz,芯片的底噪為-171 dBc/

2 電路分析與仿真

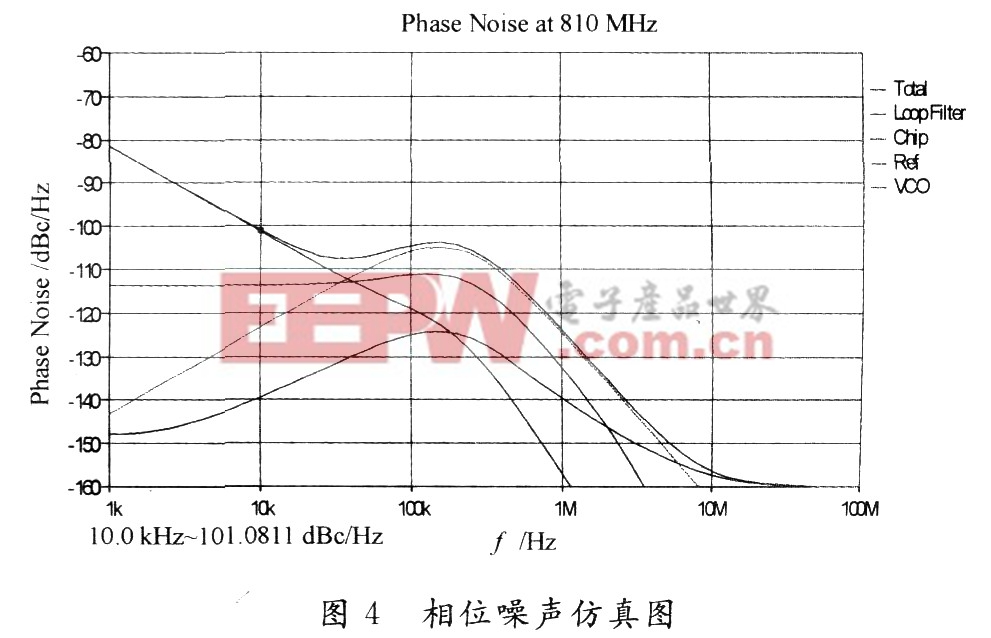

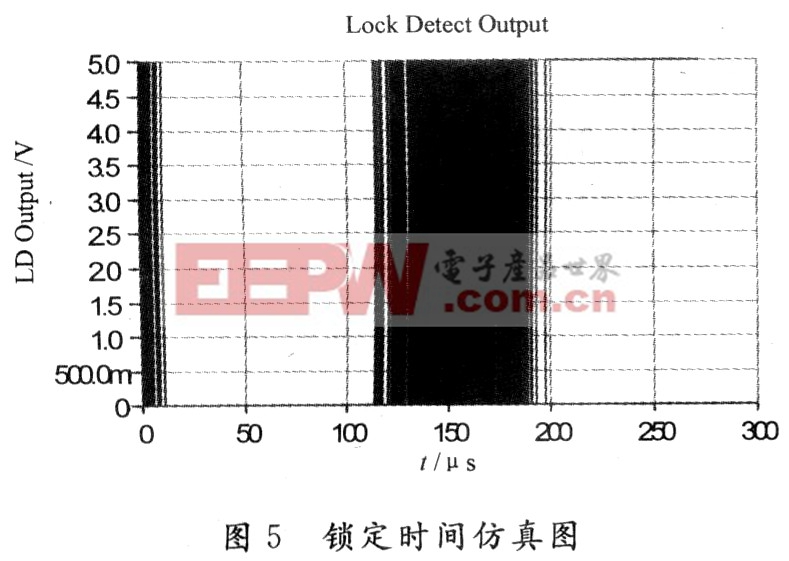

為了分析和評估提出的頻率綜合器性能,采用ADISimPLL軟件對該方案的相位噪聲模擬仿真。仿真結果如圖4,圖5所示。這里給出頻率為810 MHz,環路帶寬為120 kHz的相位噪聲仿真圖形以及鎖定時間圖形,從圖中可以看出,該方案滿足了設計目標的要求。

3 實驗及測量結果

為了檢驗文中給出的頻率綜合器性能,使用Agi-lent E4401B對掃頻源的相位噪聲、雜散進行測量,測量結果如圖6~圖8所示。594~999 MHz包含了很多頻點,測試時選擇了一系列較有代表性的點進行測量,限于篇幅,這里給出810 MHz頻點相位噪聲和雜散的測量結果。由圖可見,相噪為-92 dBc/

4 結語

介紹了一種采用DDS激勵PLL的頻率合成器,有效地克服了寬帶系統中DDS輸出頻率較低和PLL頻率分辨率低的缺點。取長補短實現頻率合成,實現了單一技術難以達到的效果。

評論