基于Matlab/DSP Builder多波形信號發生器的設計

在Simulink中進行的仿真是屬于系統驗證性質的,是對MDL文件進行的仿真,并沒有對生成的VHDL代碼進行過仿真。事實上,生成VHDL描述的是 RTL級的,是針對具體的硬件結構的,而在Matlab的Simulink中的模型仿真是算法級的,兩者之間有可能存在軟件理解上的差異。轉換后的 VHDL代碼實現可能與MDL模型描述的情況不完全相符。這就需要針對生成的RTL級VHDL代碼進行功能仿真。為此利用ModelSim對多波信號發生器進行RTL級進行仿真,以驗證多波信號發生器設計的正確性,其仿真波形如圖2所示,由此可以看出其設計是正確的[3]。

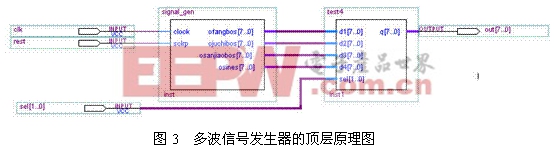

4、多波信號發生器的頂層設計及仿真結果

整體電路采用原理圖描述和VHDL語言相結合的方式構成,在Quartus II軟件中實現綜合及仿真。頂層原理圖如圖3所示,為了達到輸出信號的有選擇的目的,設計了一個多路選擇順,該多路選擇器的采用VHDL語言描述,其源代碼如下:

library ieee;

use ieee.std_logic_1164.all;

entity test4 is

port(d1,d2,d3,d4: in std_logic_vector(7 downto 0);

sel: in bit_vector(1 downto 0);

q: out std_logic_vector(7 downto 0));

end test4;

architecture rtl of test4 is

begin

process(d1,d2,d3,d4,sel)

begin

case sel is

when 00 => q = d1;

when 01 => q = d2;

when 10 => q = d3;

when 11 => q = d4;

end case;

end process;

end rtl;

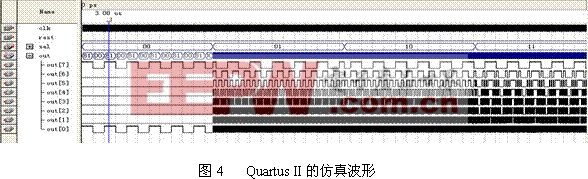

經過Quartus II的綜合與仿真,結果表明,能夠實現多種波形信號的功能。圖4是Quartus II的仿真波形。

5 結語

經過Quartus II仿真正確后,即可將項目編譯生成的編程文件下載到FPGA器件中,完成器件編程,經測試表明,電路實際工作的結果與仿真時的結果一致,達到了設計要求。

本文作者創新點在整個多波形信號發生器的設計過程中,充分利用了Matlab強大的數學計算功能來保證FPGA的設計的正確性,使整個設計非常簡單,修改靈活。設計者不至于陷于復雜的VHDL 語言編程,只要在Matlab下建立系統模型,然后對各個模塊的基本參數進行簡單設置就可以實現復雜電子系統的設計。

評論