基于SOPC的簡易誤碼率測試儀設計技術

3.4 用SignalTap嵌入式邏輯分析儀驗證設計

SignalTap允許設計者在FPGA運行期間同時監視內部信號。通過下載電纜或傳統的分析設備連接到用戶PC機上,便可以在用戶的PC機上觀察到這些信號的波形。使用SignalTap類似于使用邏輯分析儀,用戶能夠設置初始化、觸發(內部或外部)和顯示條件并觀察內部信號,以此研究運行狀態。用戶的分析參數可以被編譯為嵌入式邏輯分析儀(ELA),它和設計的其他數據一起配置FPGA。

圖5是將誤碼率測試儀硬件邏輯下載到FPGA中,用SignalTap看到的系統實際運行時的波形截圖。它顯示的是當測試代碼設定為循環代碼模式時,測試代碼從0OH到FFH之間循環發送的波形情況。信號am_clk是系統時鐘;to_7969clk是信號接收端AM7969的輸入時鐘;am_ack是信號發送端AM7968的發送反饋信號,每返回一個am_ack表示有一個數據已經發送出去;to_7969_clk是指AM7969從接收到的信號中分離出來的時鐘信號,從SignalTap可以看出有一定的延時;am_data信號是發送端AM7968發出的數據;to_7969_data是信號接收端AM7969收到的數據,可以看出,線路上有一定的延時;am_strb和tO_7969_dstrb分別是AM7968和AM7969的數據發送和接收的同步脈沖信號,本測試儀就是利用這個信號來統計測試碼發送個數和測試碼接收個數的。本文引用地址:http://cqxgywz.com/article/192153.htm

4 軟件設計

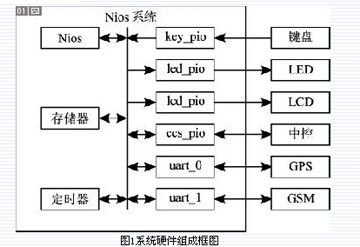

在軟件設計方面,本著簡單易用的原則進行,在盡可能滿足實際使用需求的同時,提供友好的人機交互接口。下面分別介紹一下軟件的開發環境(Nios II IDE)和軟件開發設計。

Nios II集成開發環境(IDE)是Nios II系列嵌入式處理器的基本軟件開發工具。所有軟件開發任務都可以在Nios IIIDE下完成,包括編輯、編譯和調試程序。Nios II IDE提供了一個統一的開發平臺,用于所有Nios II處理器系統。僅僅通過1臺PC機、1片A1tera公司的FPGA以及1根JTAG下載電纜,軟件開發人員就能夠往Nios II處理器系統寫入程序,并與Nios II處理器系統進行通信。Nios II IDE為軟件開發提供4個主要功能:工程管理器、編輯器和編譯器、調試器、閃存編程器。

為了便于大批量地測量線路的誤碼率,方便用戶使用,設計了“自動測量”模式。該模式的各種參數是用戶預先設置好的,其中包括測試模式、測試速率、測試代碼以及時間閾值或者數量閾值。這樣,用戶在檢測大批量的通信電纜時,就不需要重復進行繁瑣的參數設置了。表1是需要用戶設置的參數,圖6為主程序流程。

5 結 論

本文結合石油勘探儀器車與外部設備連接電纜測試的實際,提出了一種采用SOPC技術的誤碼率測試儀整體設計實現方案。能夠較好地滿足測量要求,接口友好,并且在誤碼率上給予用戶比較客觀的評價。設備具有體積小、重量輕、功耗低、成本低、性能高、易于軟硬件升級等優點。比起其他專業誤碼率測試設備,在經濟性、實用性方面表現得尤為突出。

評論