基于AD7762和FPGA的數據采集系統設計

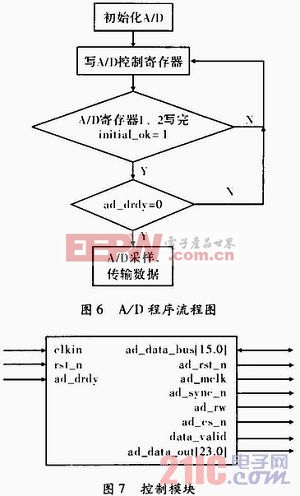

控制A/D的程序流程圖如圖6所示。程序編譯后生成的A/D轉換器的控制模塊如圖7所示。本文引用地址:http://cqxgywz.com/article/193417.htm

模塊中ad_data_bus[15.0]與FPGA的IO口進行連接。ad_rst_n是A/D的復位信號,而rst_n是系統的復位信號。ad_mclk外接40 MHz晶振,進入A/D后經過寄存器設置進行二分頻。ad_sync是同步信號,可以同步多片ADC,此處不操作。

將程序通過FPGA的JTAG口下載到硬件系統,進行仿真得到的A/D模塊仿真結果如圖8所示。

對A/D進行仿真。從仿真圖中可以看出,A/D產生![]() 低電平后才開始根據

低電平后才開始根據![]() 的高低電平控制傳輸數據。

的高低電平控制傳輸數據。

3.3 FIFO數據緩存模塊

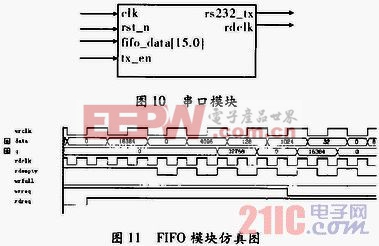

FIFO用于存儲FPGA接收的A/D采集的數據,FIFO模塊的讀時鐘受前端A/D模塊巾的data_valid信號控制,寫時鐘由后面的串口模塊產生,已達到FIFO數據讀取與串口傳輸的數據一致。保證數據準確地通過串口傳輸到上位機。FIFO的讀寫控制信號分別由wrfull和rdempty控制,FIFO模缺如圖9所示。

3.4 串口數據傳輸模塊

串口模塊的開啟和關閉信號tx_en受FIFO模塊的讀信號rdreq控制。

4 結束語

數據采集系統設計中,AD7762內部設置差分放大器和靈活設置的寄存器,使得外部的電路設計簡單且成本低。FPGA控制更為靈活方便,若想改變A/D的工作狀態只需要更改寄存器的設置內容即可。減少外部控制線的數量,使系統減小干擾,更為可靠。若將此系統作為音頻信號分析系統的前端,將使整個系統的穩定度及精確度得到提高。

評論