使用LabVIEW FPGA模塊設計IP核

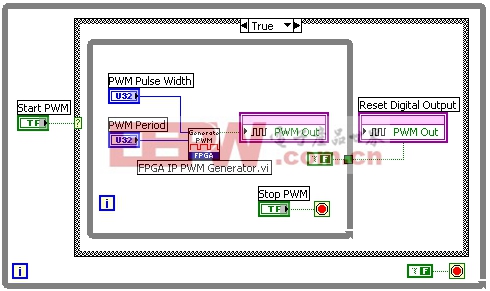

圖8:展示PWM發生器IP的使用方法的VI范例

總結

如果創建的IP代碼模塊靈活且易于使用,那么LabVIEW FPGA IP代碼模塊可以在應用開發中提供顯著的優勢和節約。該文檔所介紹的指導方針將有助于確保IP可以方便地復用并無須為單個應用進行定制處理。

下面是在開發任何LabVIEW FPGA IP過程中應當遵循的指導方針的總結列表:

I/O資源不應嵌入在IP代碼模塊的框圖中。

請勿在IP中使用項目引用的存儲器讀寫函數或FIFO讀寫函數。如可能,使用一個VI scoped存儲塊或FIFO(LabVIEW 8.20)。

文檔化表述IP中存儲器(存儲器拓展例程存儲塊、FIFO和查詢表等)的所有使用。在IP的分布中包含任何存儲器拓展例程存儲塊VI。

不要在IP中包含任何循環結構或等待/循環定時器函數,除非這便是該IP的主要目標。

在IP中使用局部變量存儲狀態信息。

文檔化表述IP的任何非正常的定時行為。

評論